### Customer Engineering Division

MICROPROCESSOR MANUAL OF MASS STORAGE DEVICES

·

# Customer Engineering Division

# MICROPROCESSOR MANUAL OF MASS STORAGE DEVICES

© Wang Laboratories, Inc., 1975

#### NOTICE:

This document is the property of Wanq Laboratories, Inc. Information contained herein is considered company proprietary information and its use is restricted solely to the purpose of assisting you in servicing Wang products. Reproduction of all or any part of this document is prohibited without the consent of Wang Laboratories.

LABORATORIES, INC.

#### TABLE OF CONTENTS

| 1. | INTR | ODUCTIO        | N '                                                | 1          |

|----|------|----------------|----------------------------------------------------|------------|

| 2. | MODE | L 22 <b>70</b> | MICROPROCESSOR                                     | 1          |

|    | 2.1  | MODEL          | 2270 SIMPLIFIED THEORY OF OPERATION                | 1          |

|    |      | 2.1.1          | Read Only Memory                                   | 3          |

|    |      | 2.1.2          | Random Access Memory                               | 4          |

|    |      | 2.1.3          | Arithmetic/Logic Unit                              | 6          |

|    |      | 2.1.4          | Register Structure                                 | 6          |

|    | 2.2  | THE IN         | STRUCTION SET - HARDWARE CONTROL VIA SOFTWARE      | 9          |

|    |      | 2.2.1          | General                                            | 9          |

|    |      | 2.2.2          | Instruction Categories                             | 10         |

|    |      | 2.2.3          | Instruction Set Summary                            | 15         |

|    |      |                | 2.2.3.1 Introduction                               | 15         |

|    |      |                | 2.2.3.2 Instruction Set Examples                   | 22         |

|    |      |                | 2.2.3.3 Typical Microprogram                       | 31         |

|    |      | 2.2.4          | Model 2270 Microprogram                            | 36         |

|    | 2.3  | HARDWA         | RE OPERATIONAL THEORY                              | 52         |

|    | •    | 2.3.1          | Introduction                                       | 52         |

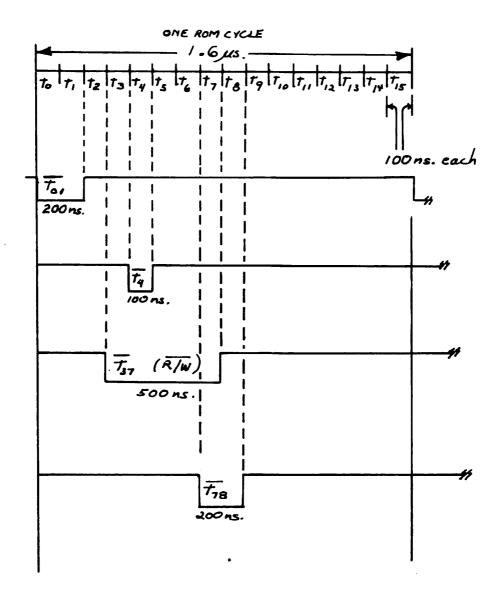

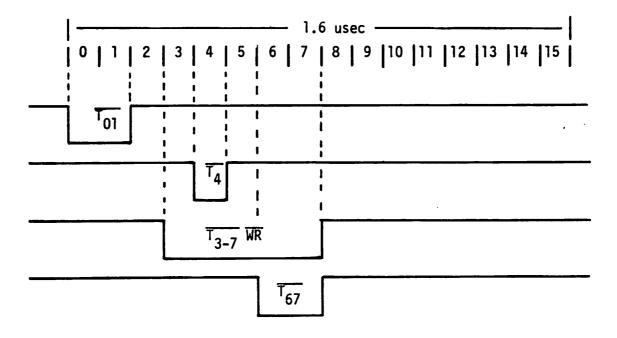

|    |      | 2.3.2          | Timing                                             | 52         |

|    |      | 2.3.3          | Input to Microprocessor from CPU                   | <b>5</b> 3 |

|    |      | 2.3.4          | Output of Microprocessor to Disk                   | 54         |

|    |      | 2.3.5          | Input from Disk to Microprocessor                  | 55         |

|    |      | 2.3.6          | Output from Microprocessor to CPU                  | 55         |

|    |      | 2.3.7          | Disk Control Operations                            | 55         |

|    |      | 2.3.8          | Sector Counter .                                   | 57         |

|    |      | 2.3.9          | Cyclic Redundancy Check                            | 57         |

|    |      | 2.3.10         | Format Routine                                     | 57         |

|    | 2.4  | TROUBL         | ESHOOTING PROCEDURES                               | 59         |

|    |      | 2.4.1          | Introduction                                       | 59         |

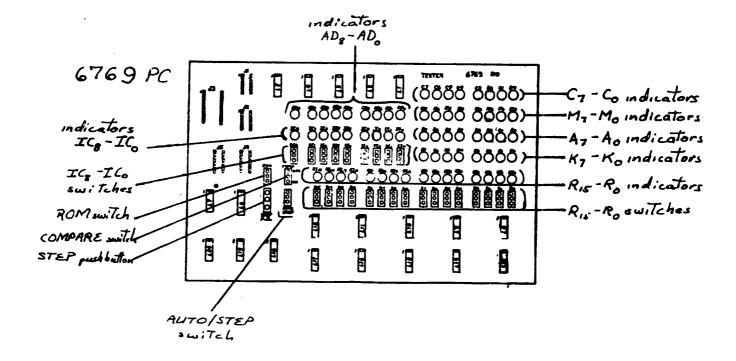

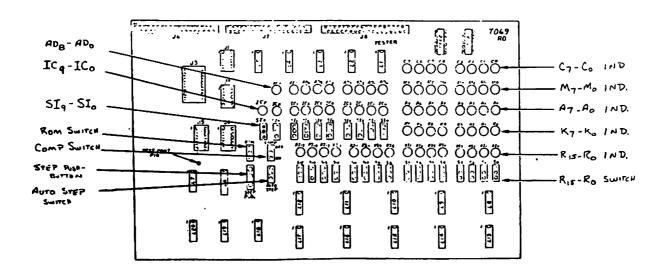

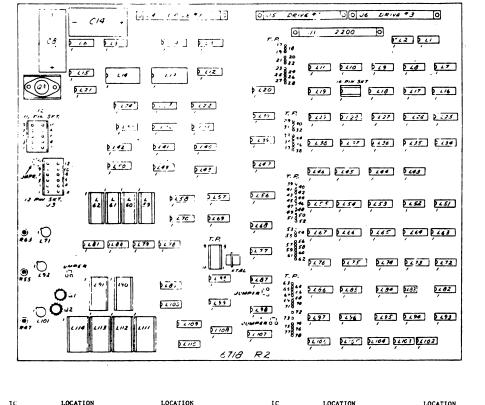

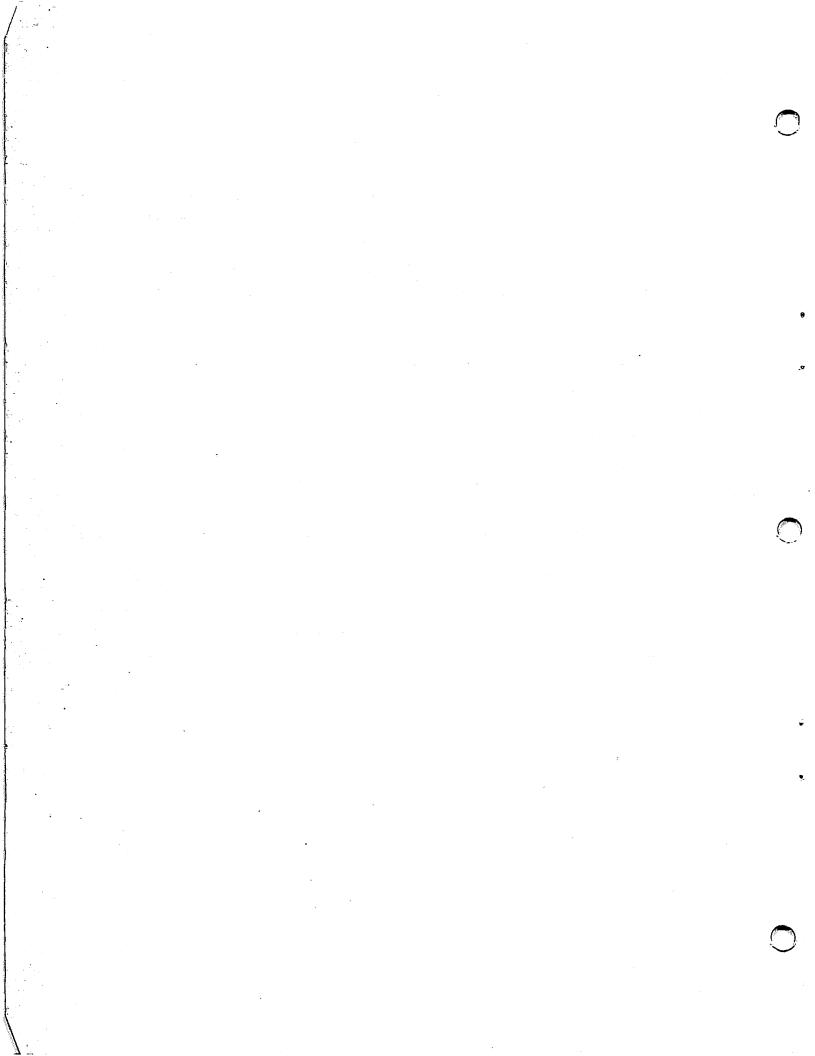

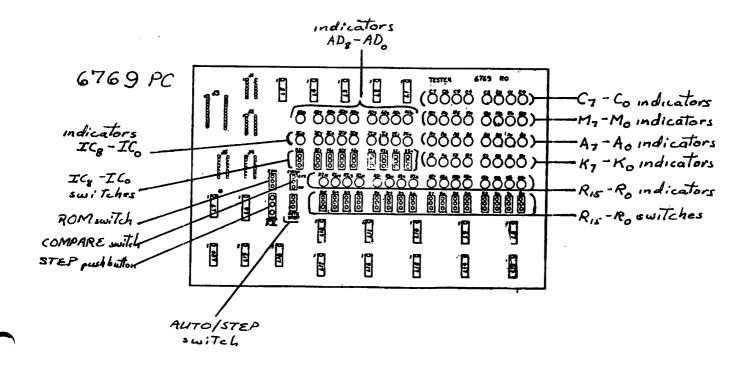

|    |      | 2.4.2          | Familiarization with Physical Layout of Test Units | 59         |

|    |      | 2.4.3          | Operational Use of Test Units                      | 61         |

|    |      | 2.4.4          | 6718/7018 Repair                                   | 63         |

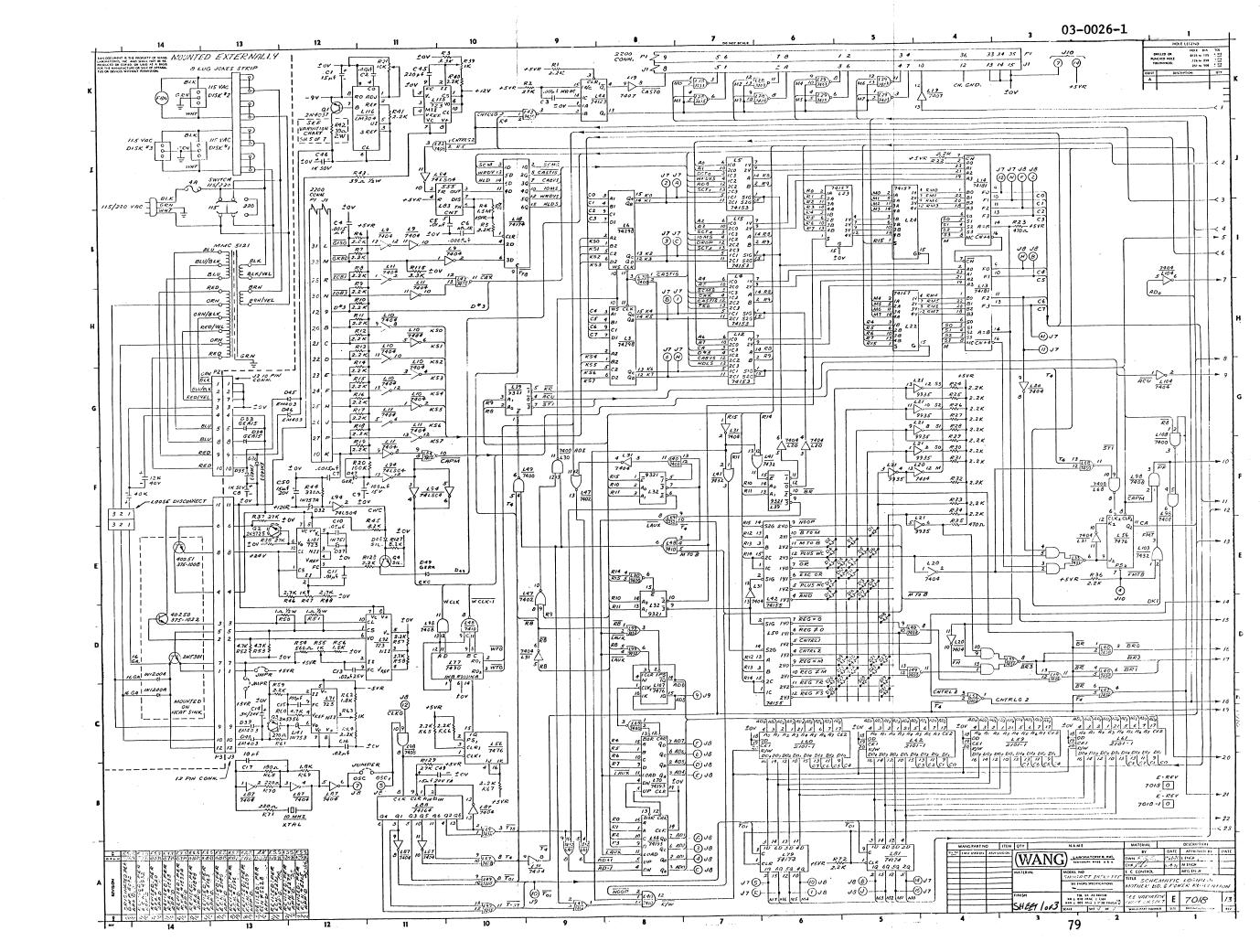

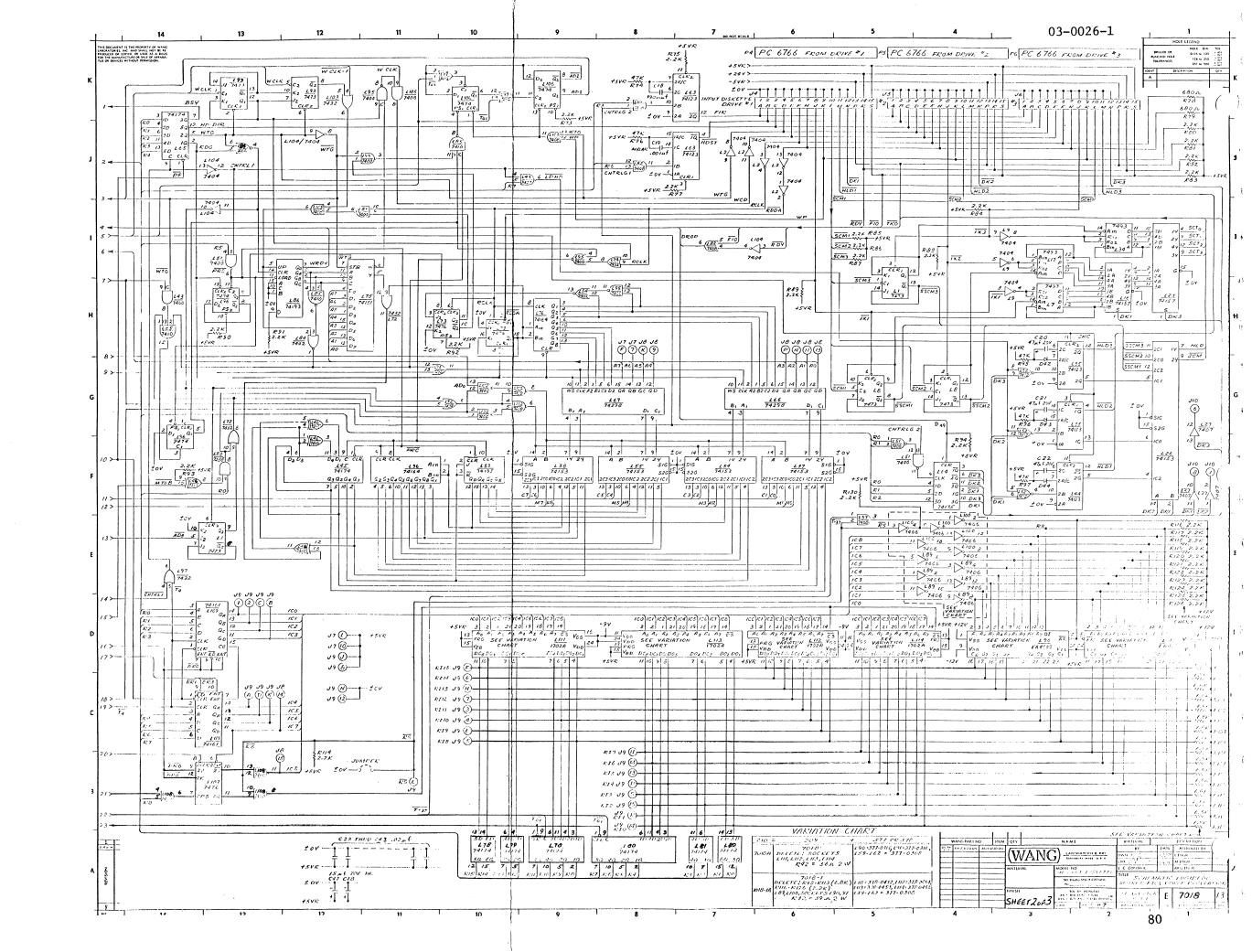

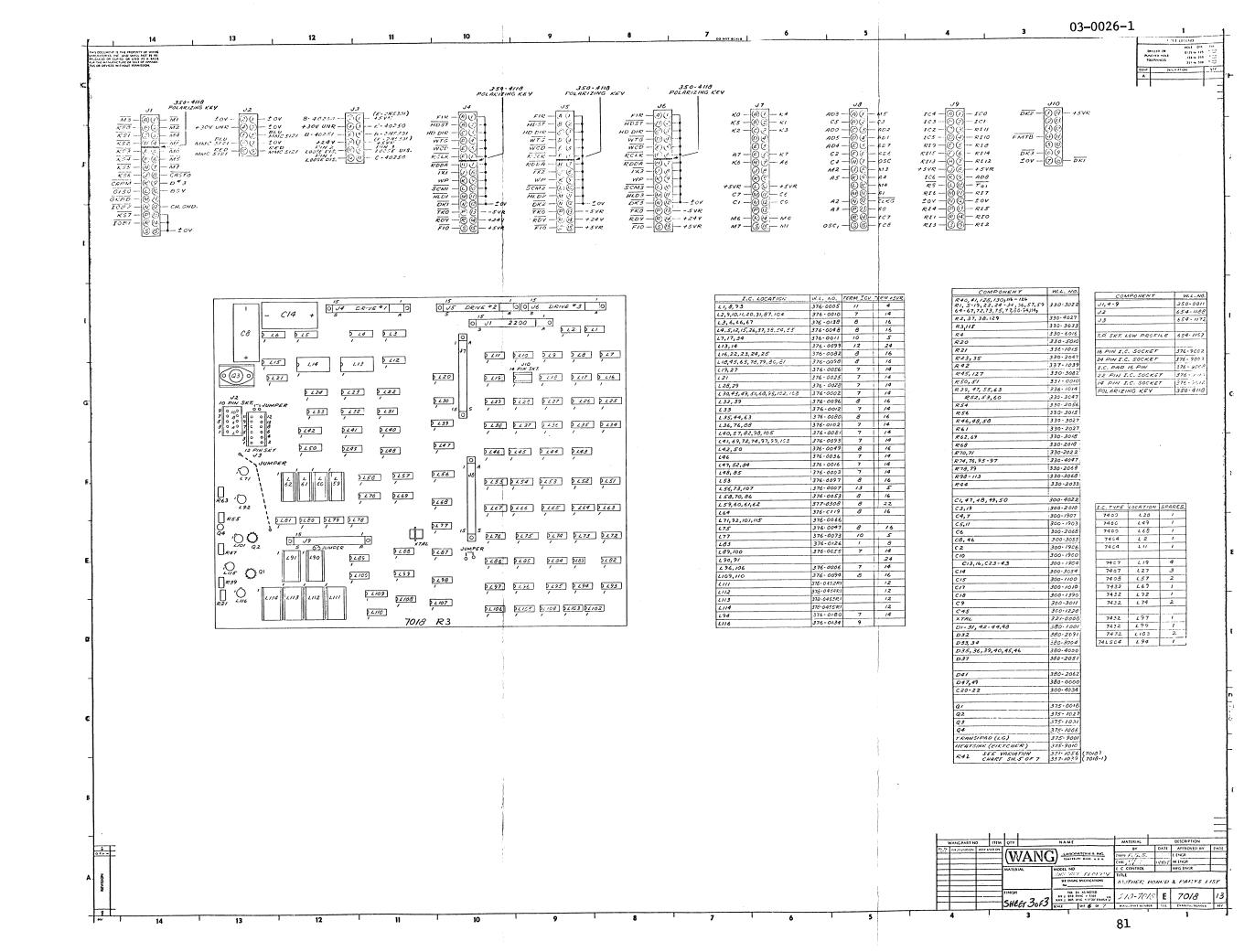

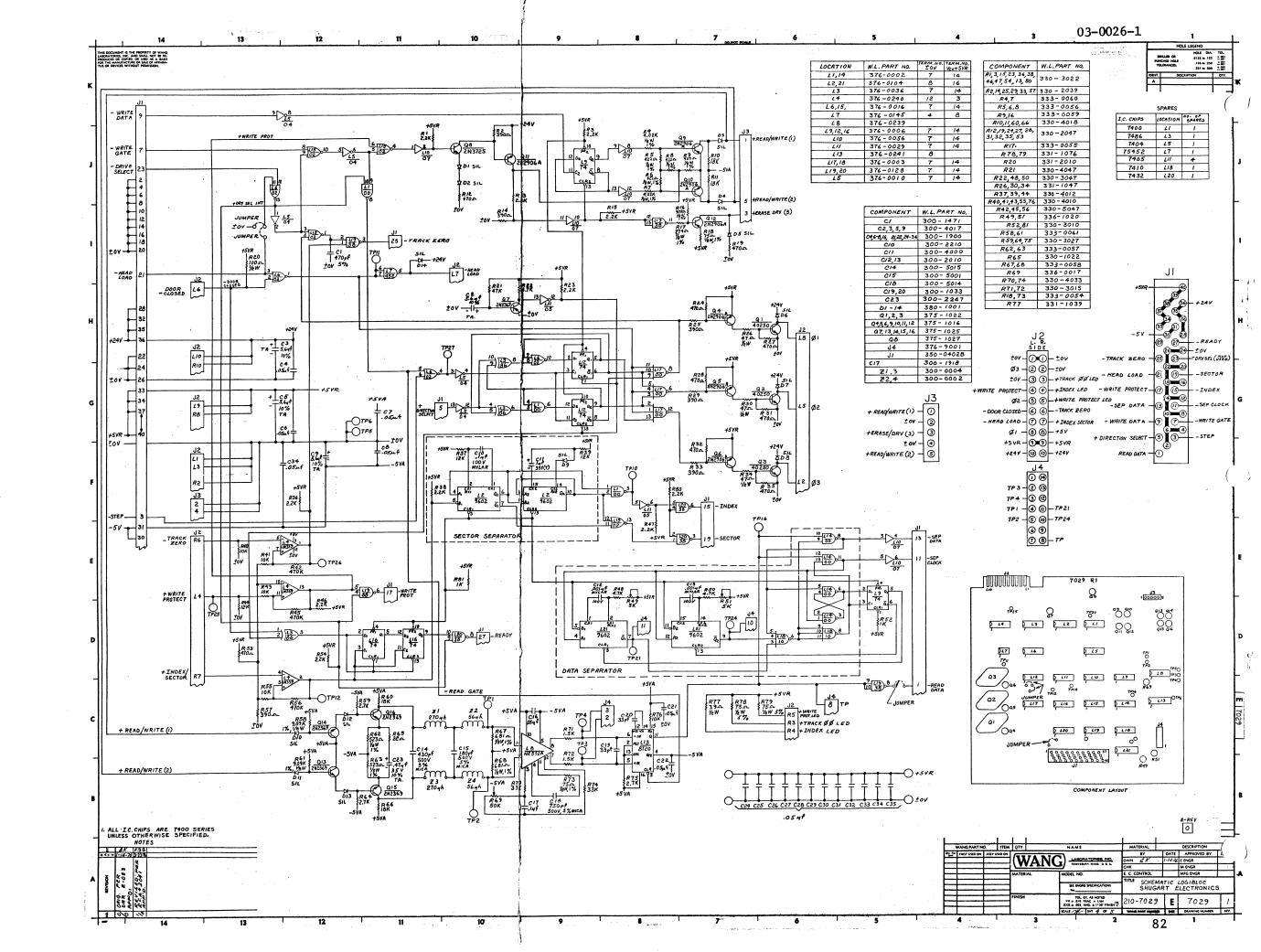

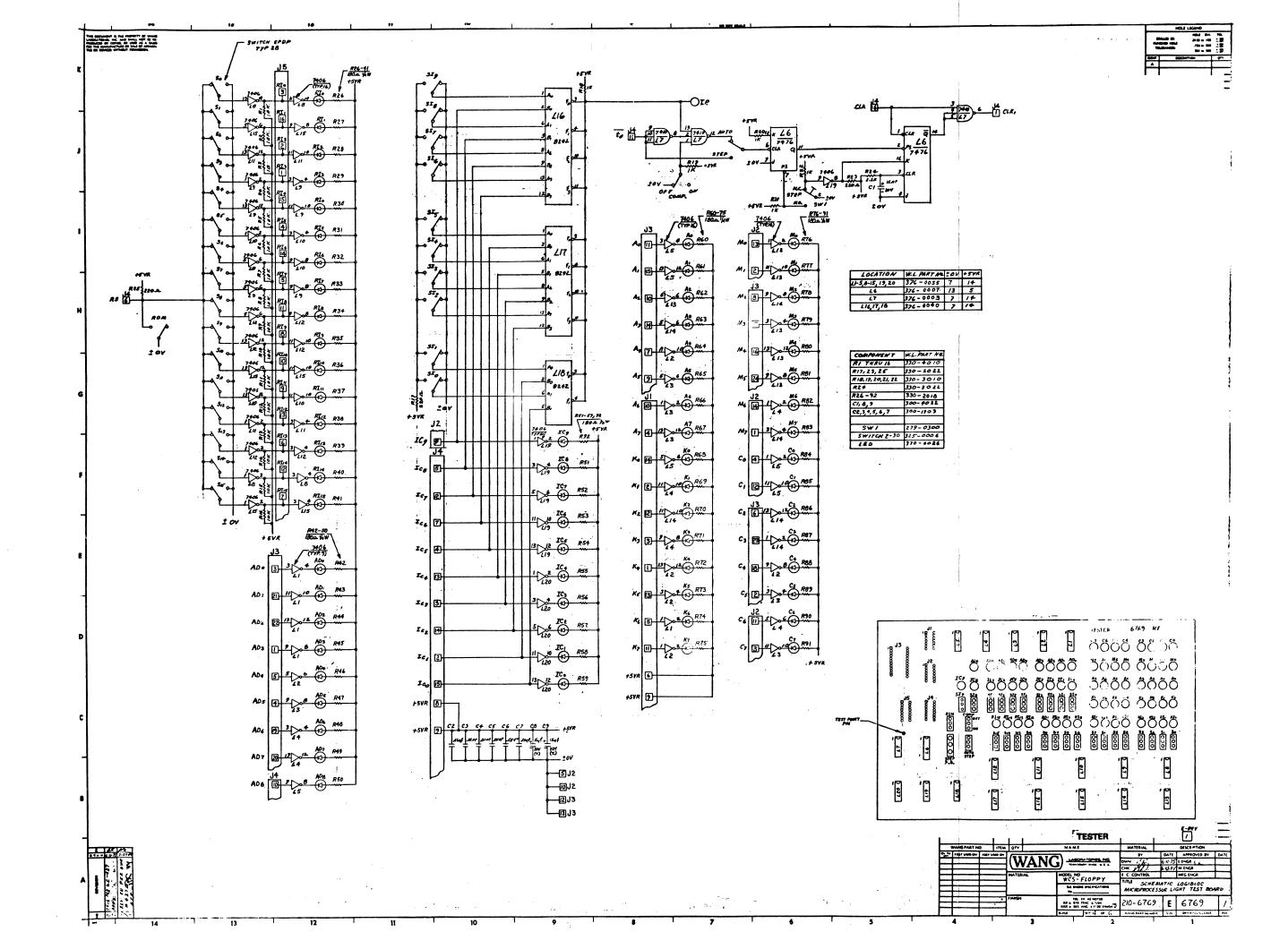

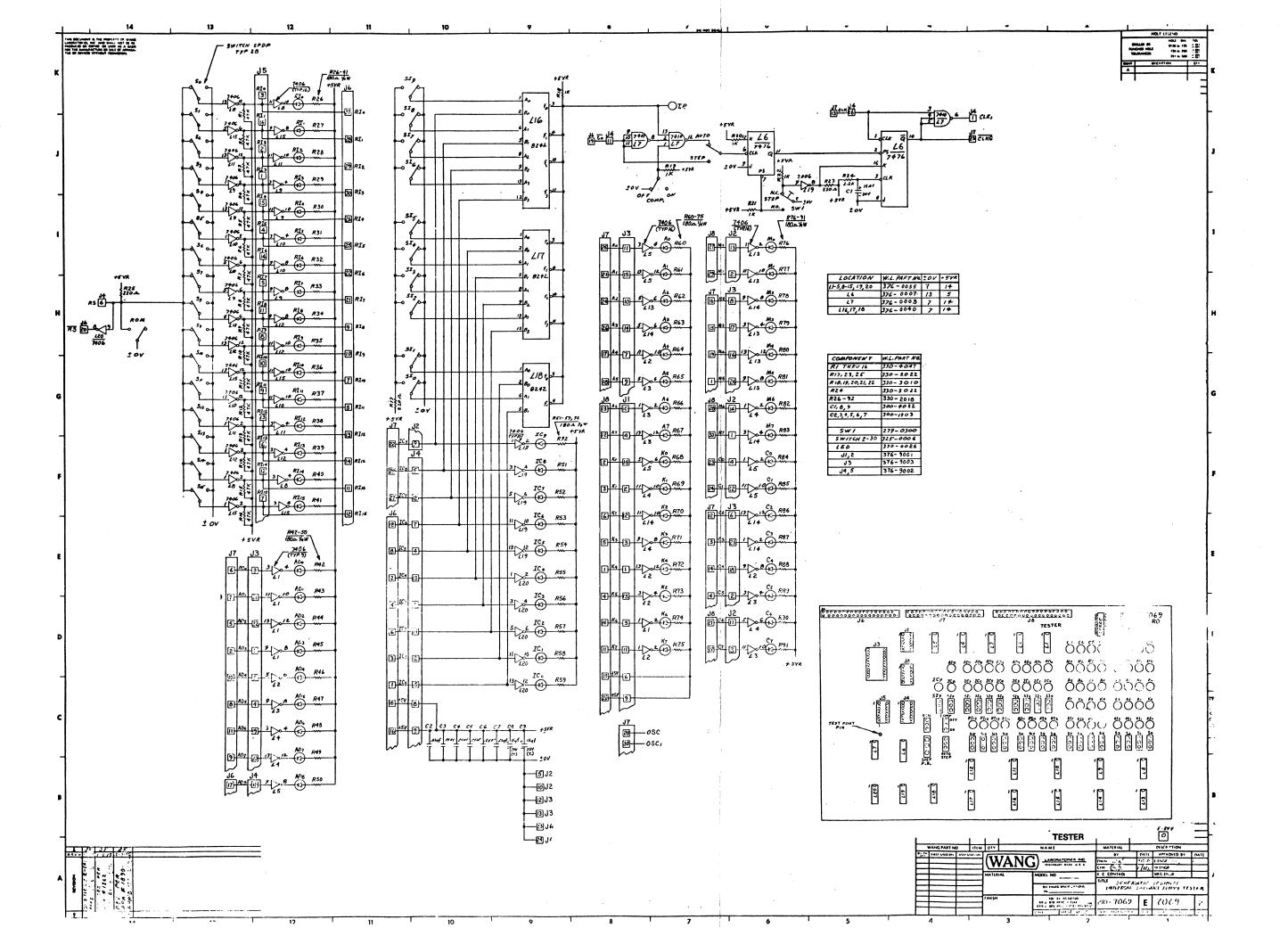

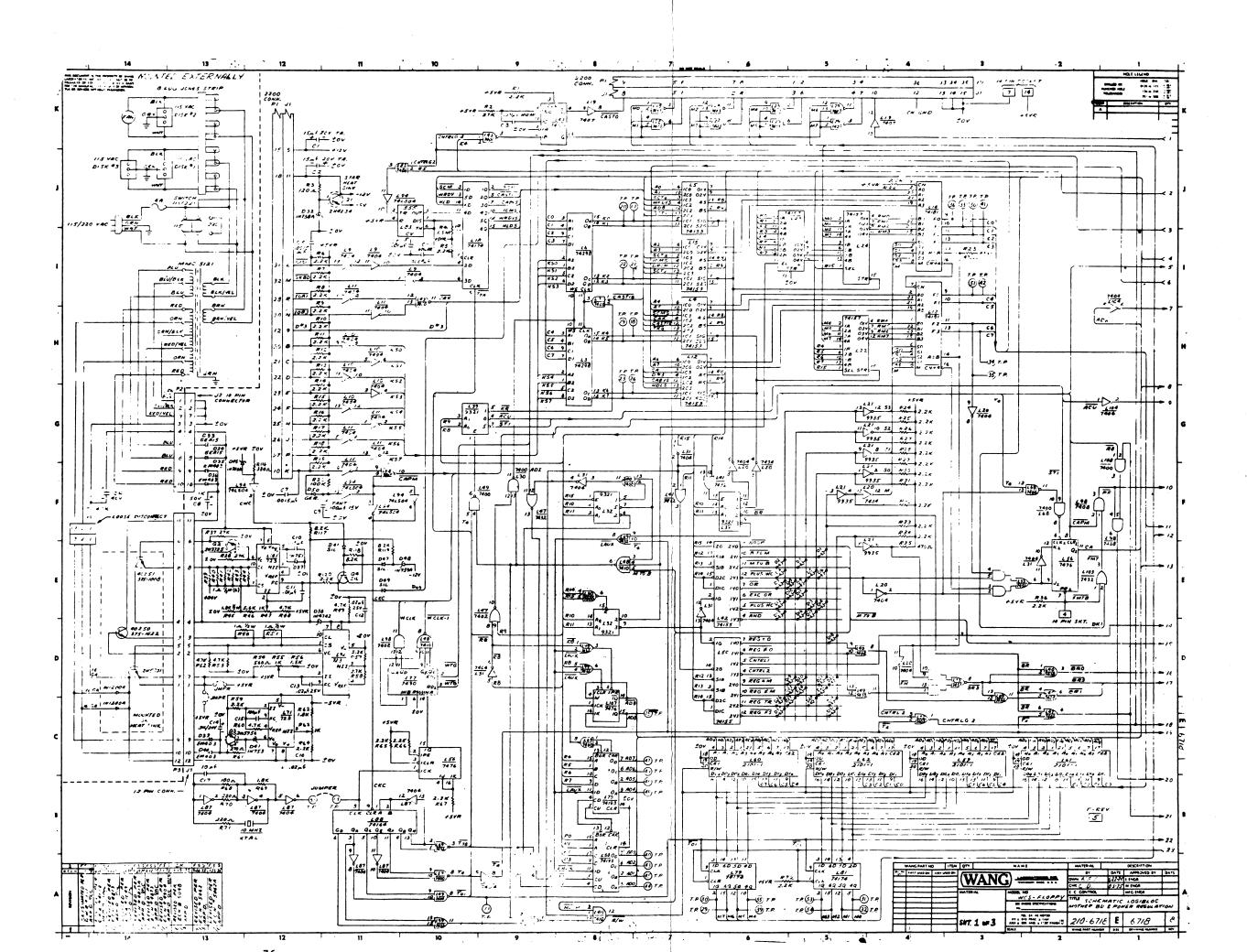

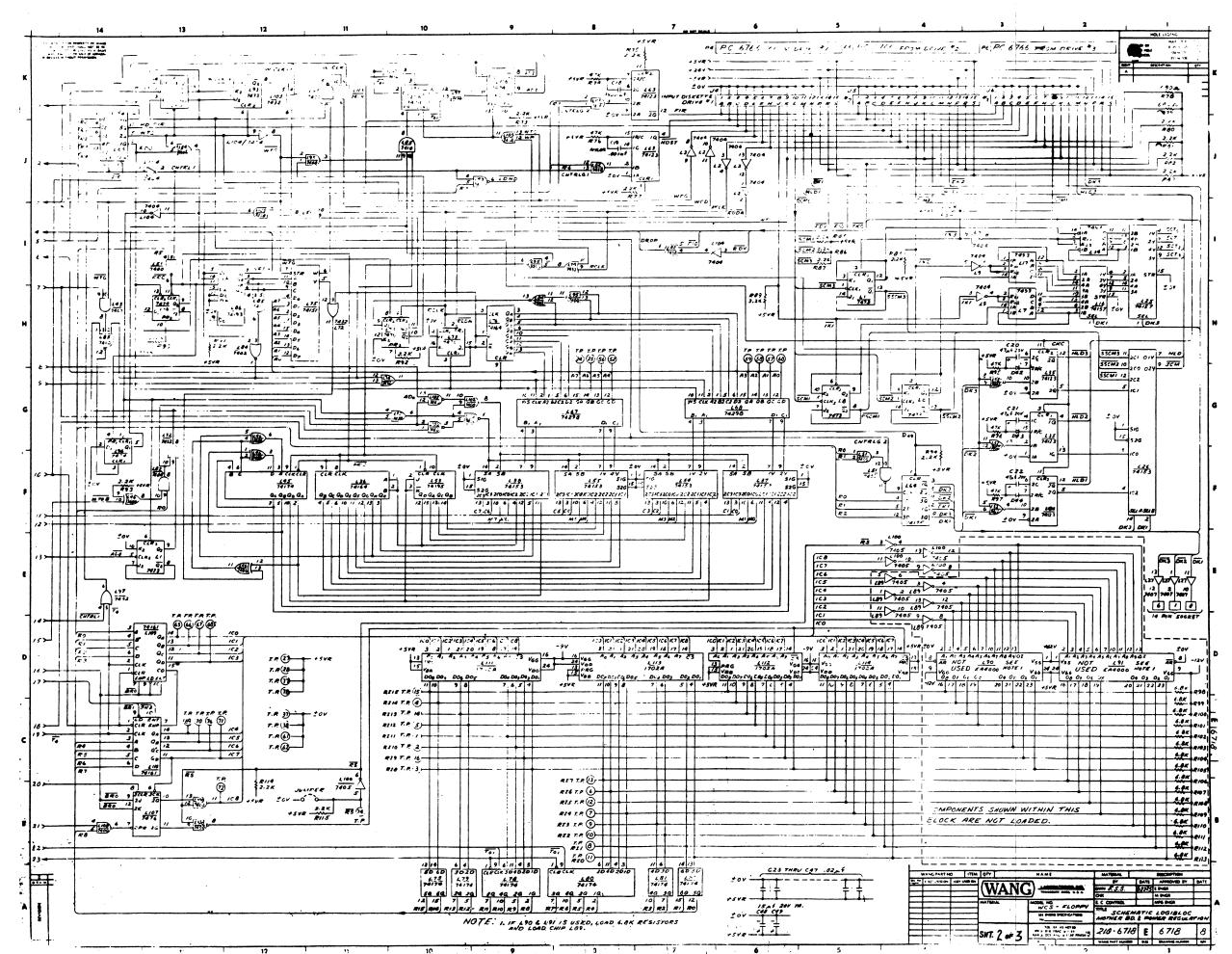

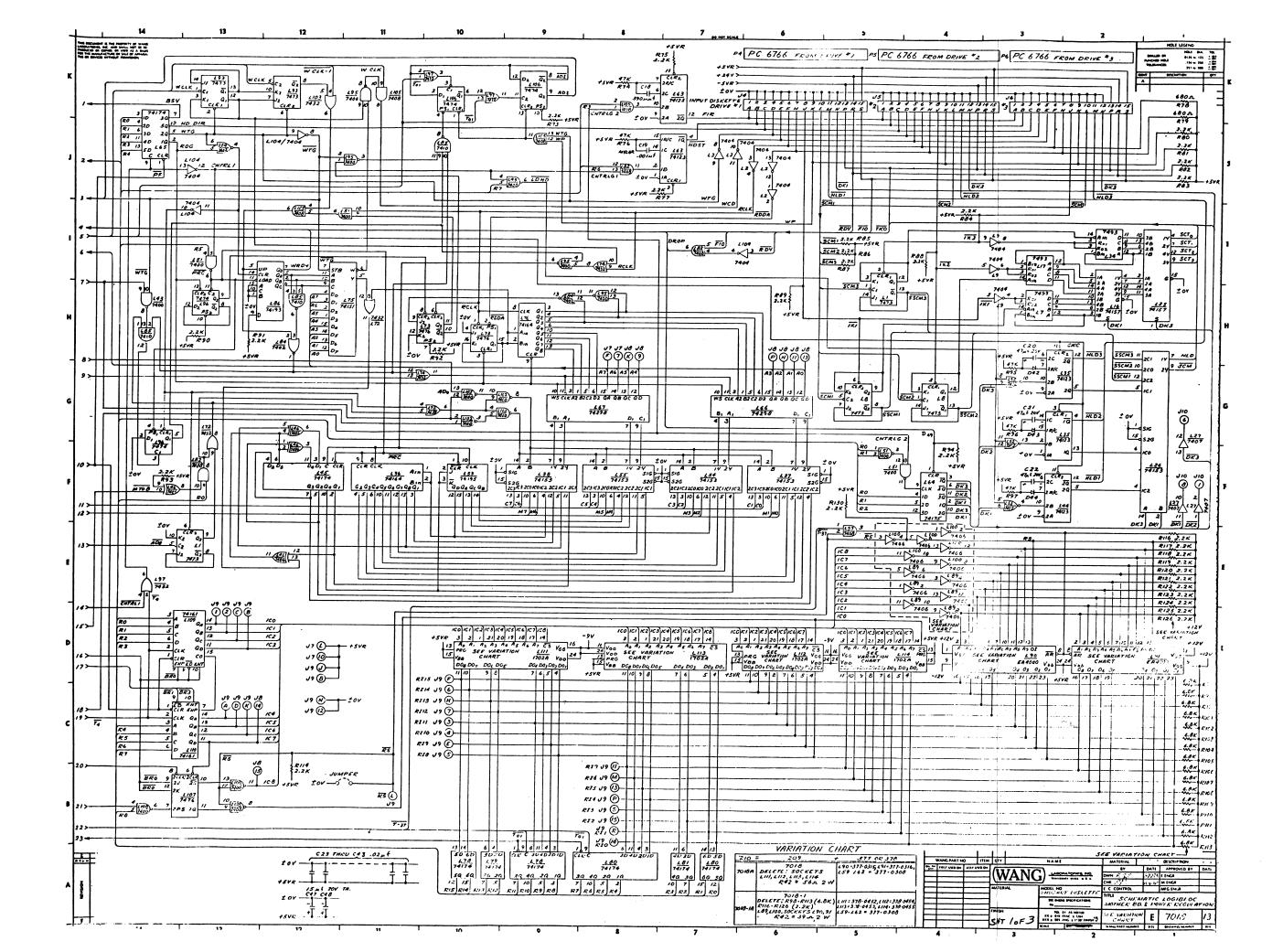

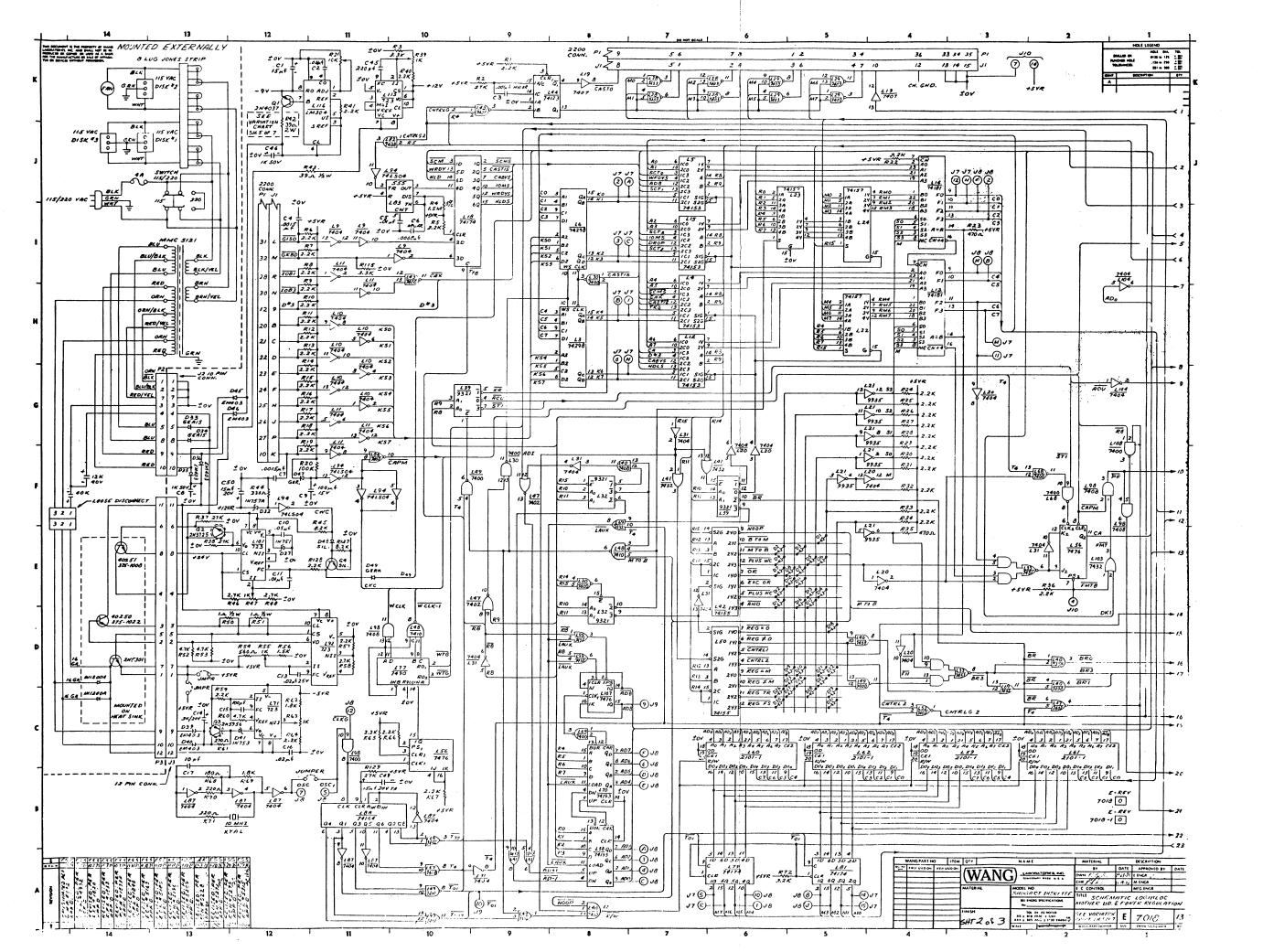

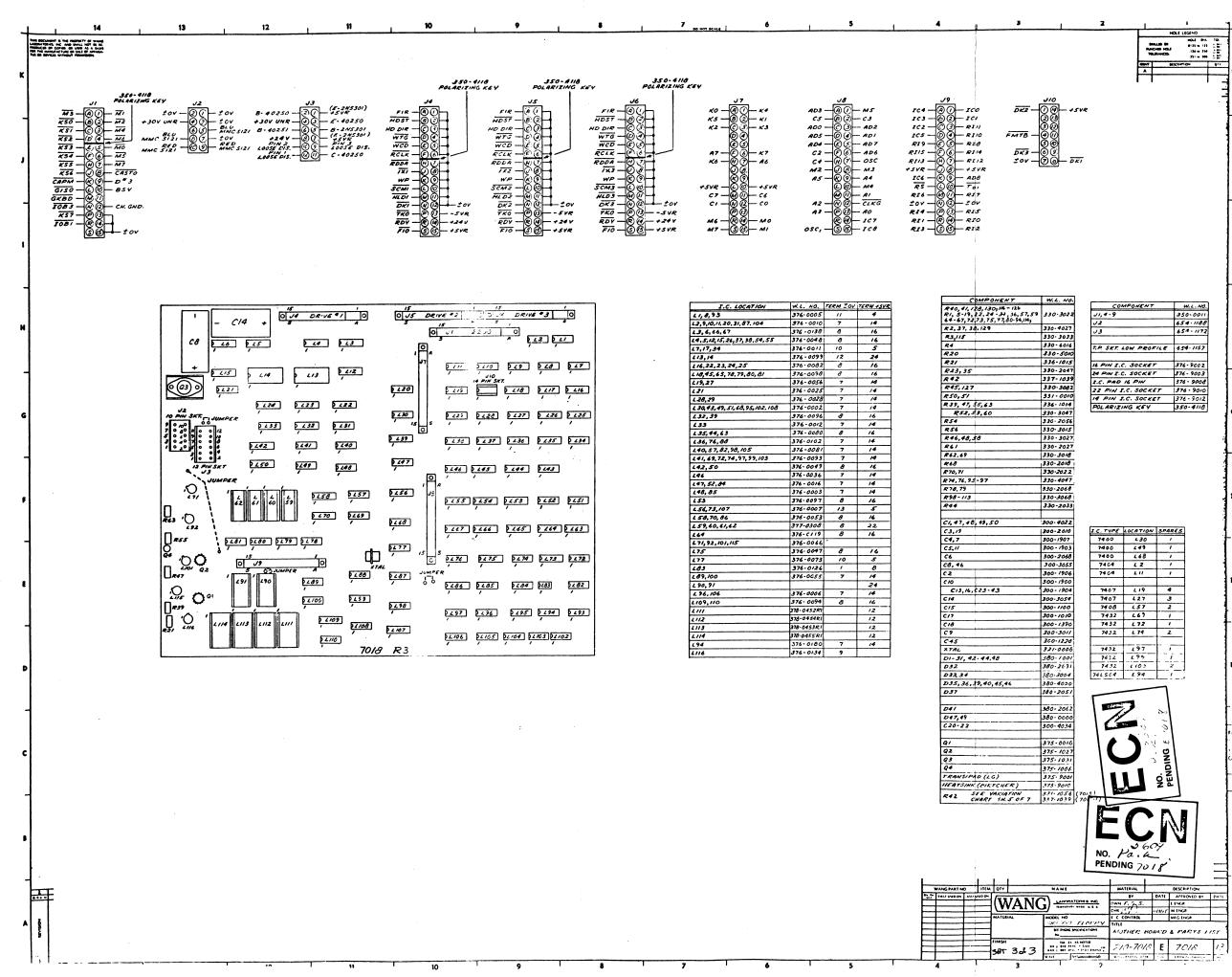

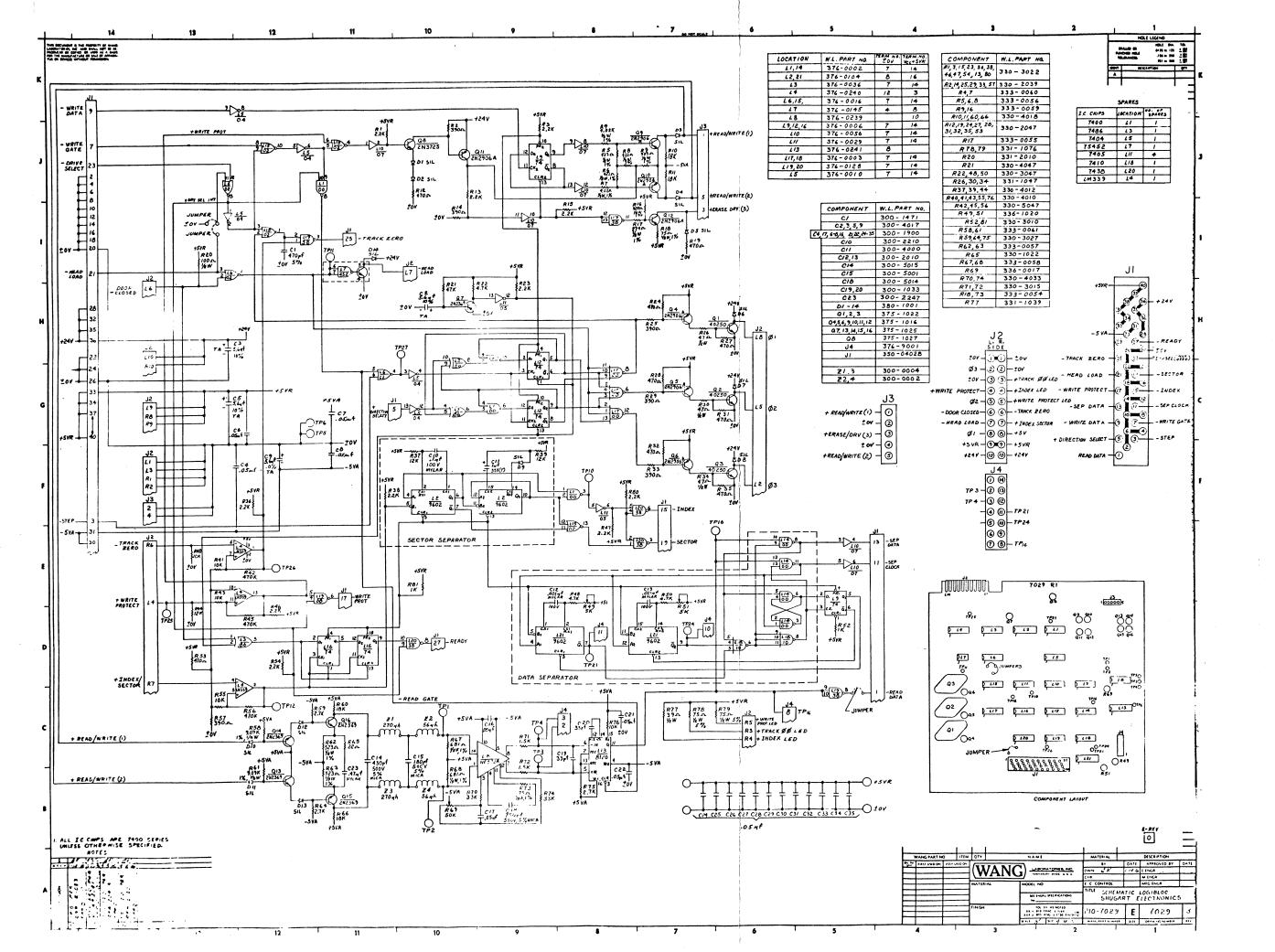

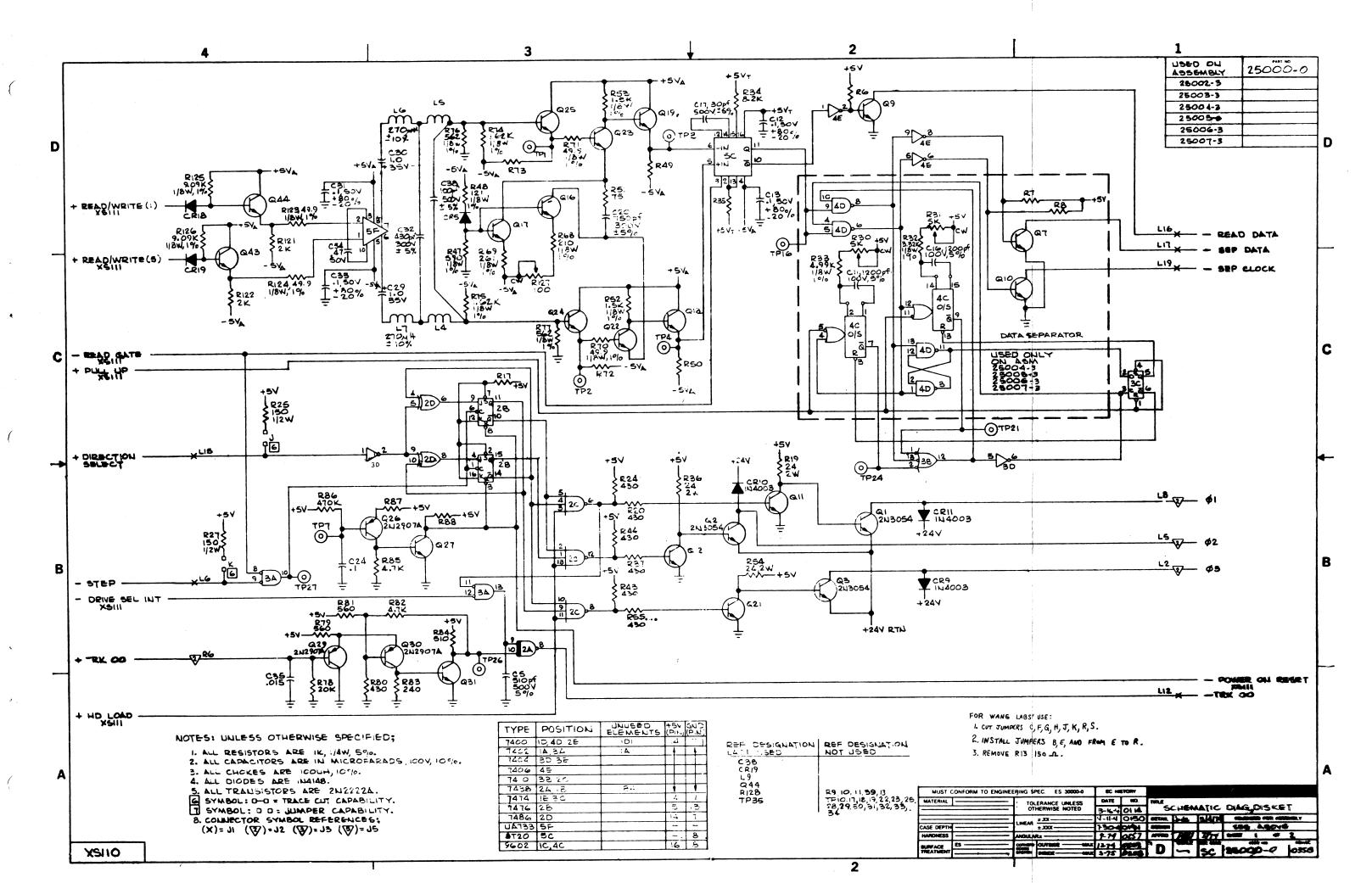

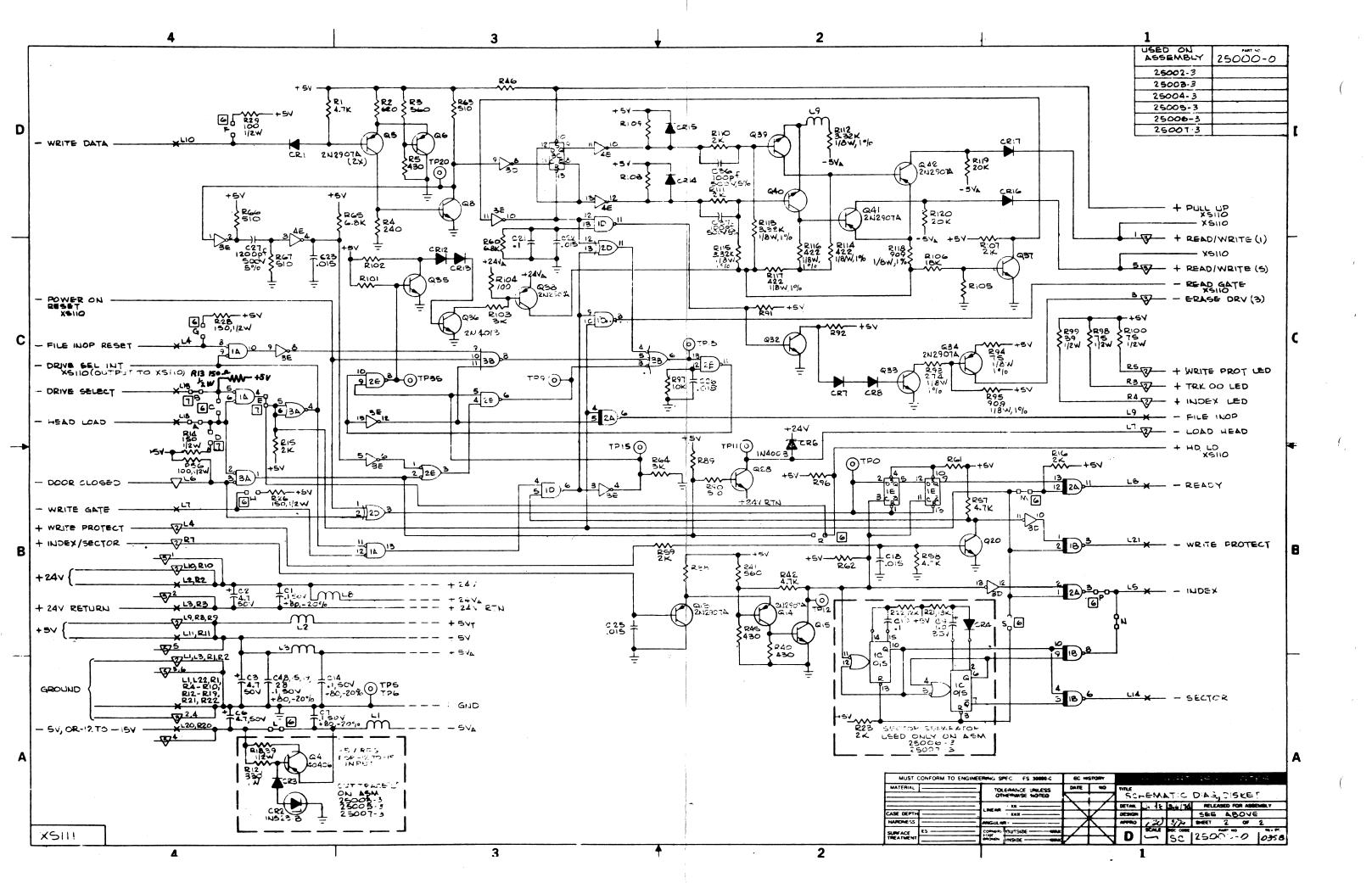

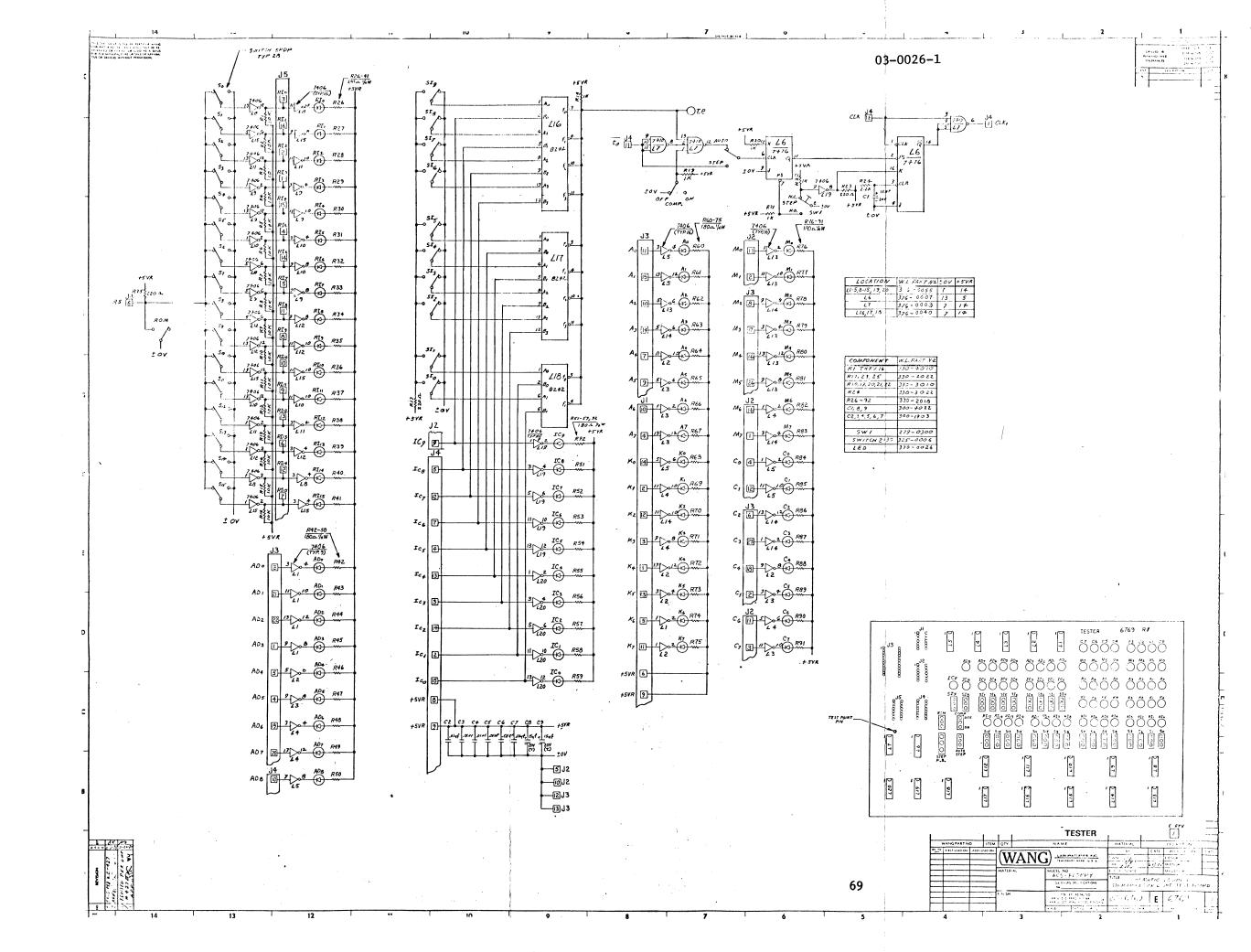

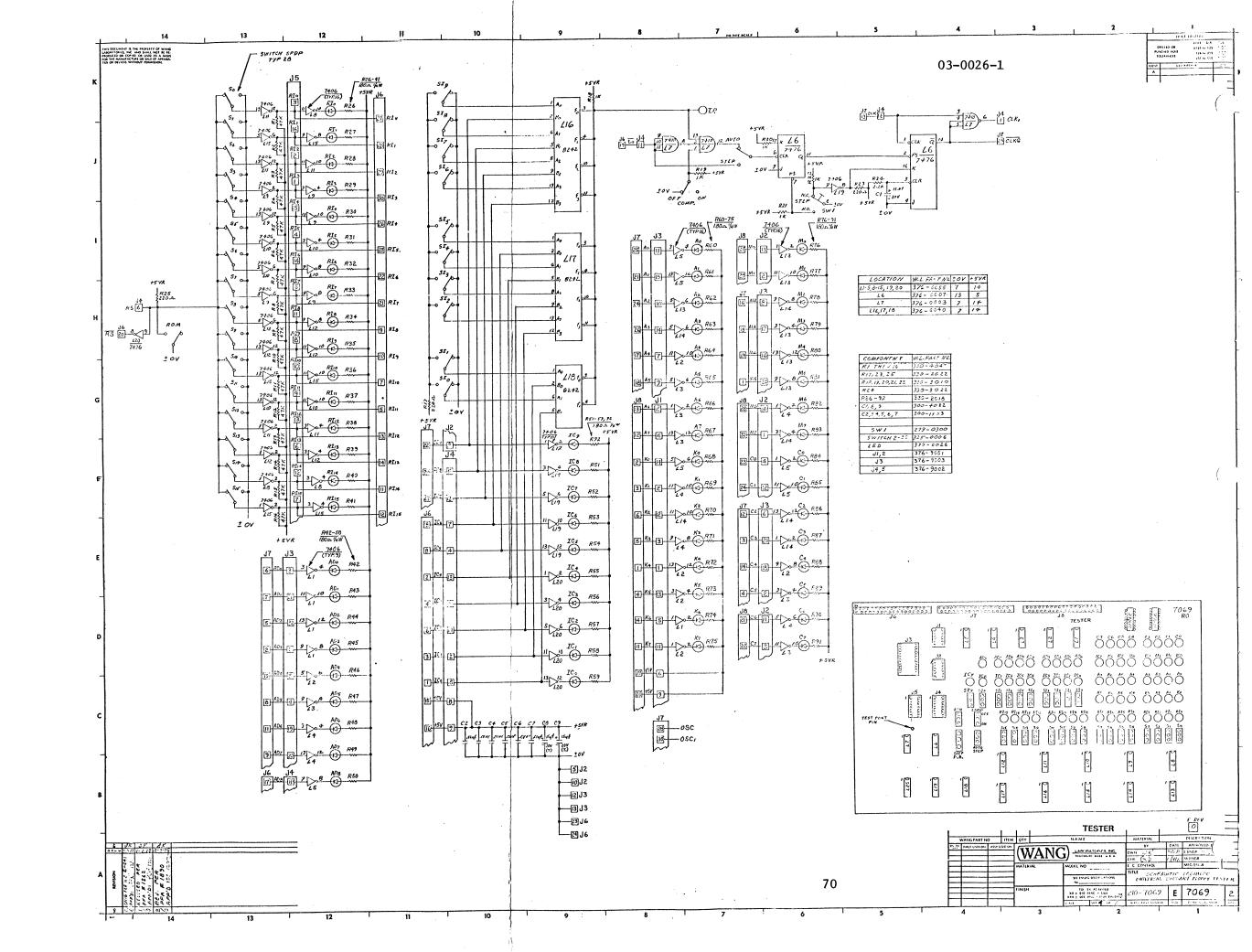

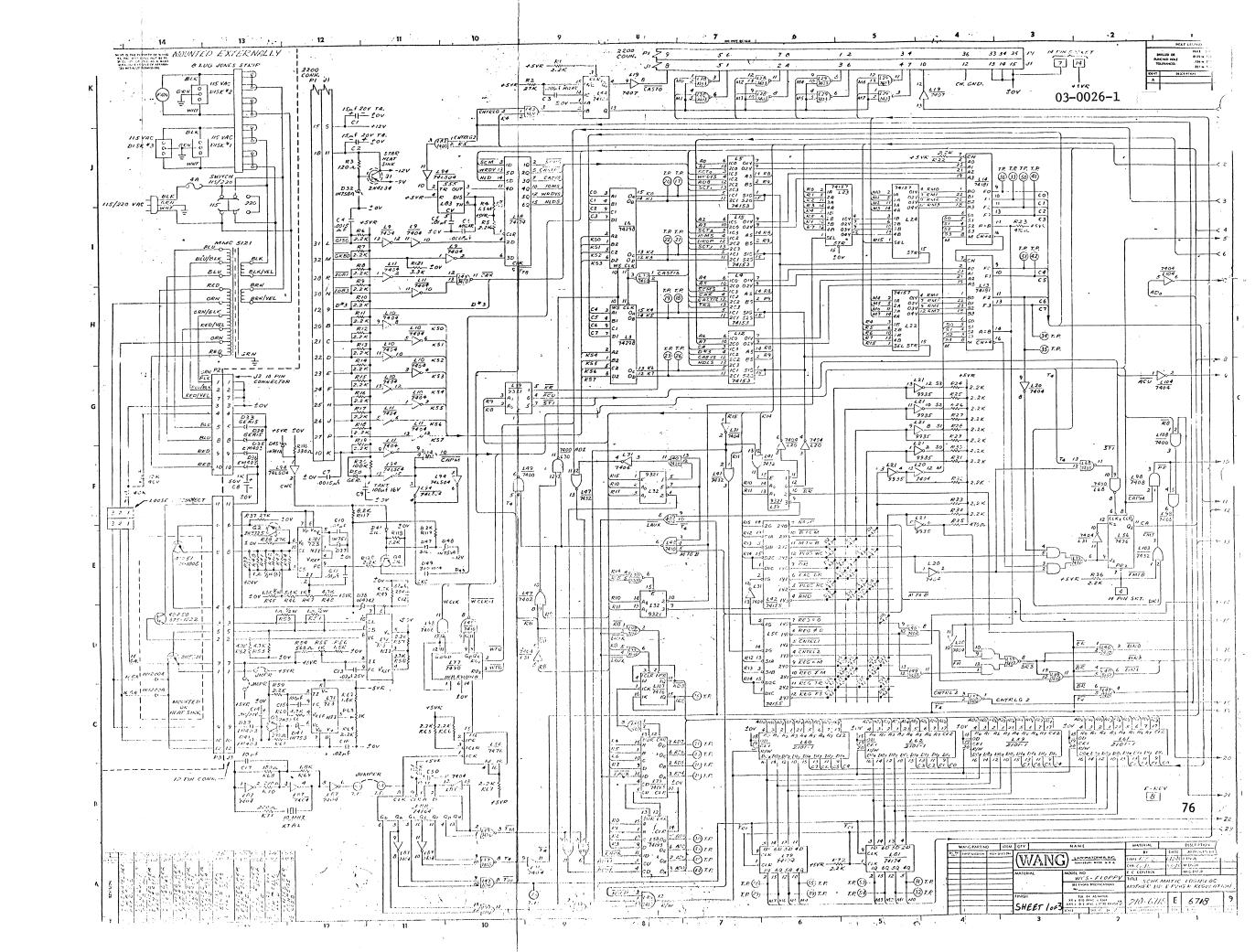

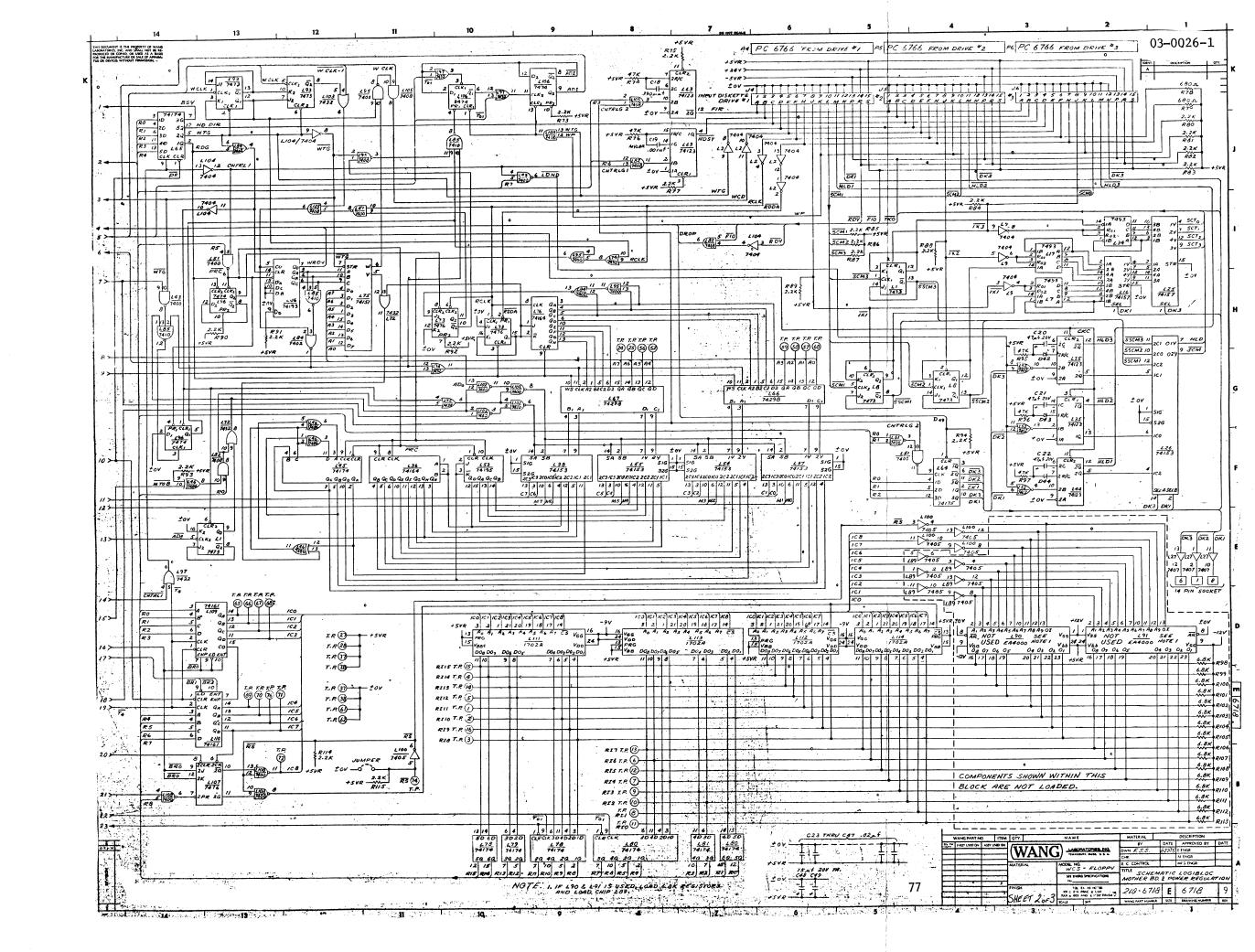

|    | 2.5 MODE  | EL 2270 DIAGRAM AND SCHEMATICS   | 72  |

|----|-----------|----------------------------------|-----|

|    | 2.6 MODE  | EL 2270 SIGNAL MNEMONICS         | 85  |

| 3. | MODEL -30 | O, -40 AND -60 MICROPROCESSORS   | 93  |

|    | 3.1 6295  | 5 I/O TERMINATOR                 | 93  |

|    | 3.2 6395  | 5/6537 I/O TERMINATOR            | 93  |

|    | 3.3 6296  | 5 DISK CONTROLLER                | 95  |

|    | 3.4 6297  | 7 DISK CONTROLLER                | 97  |

|    | 3.5 6298  | 8 ROM/RAM                        | 101 |

|    | 3.6 6299  | 9 DISK CONTROLLER                | 103 |

|    | 3.7 6399  | 9 DISK CONTROLLER                | 106 |

|    | 3.8 MODI  | EL 2230, 2240 AND 2260 MNEMONICS | 106 |

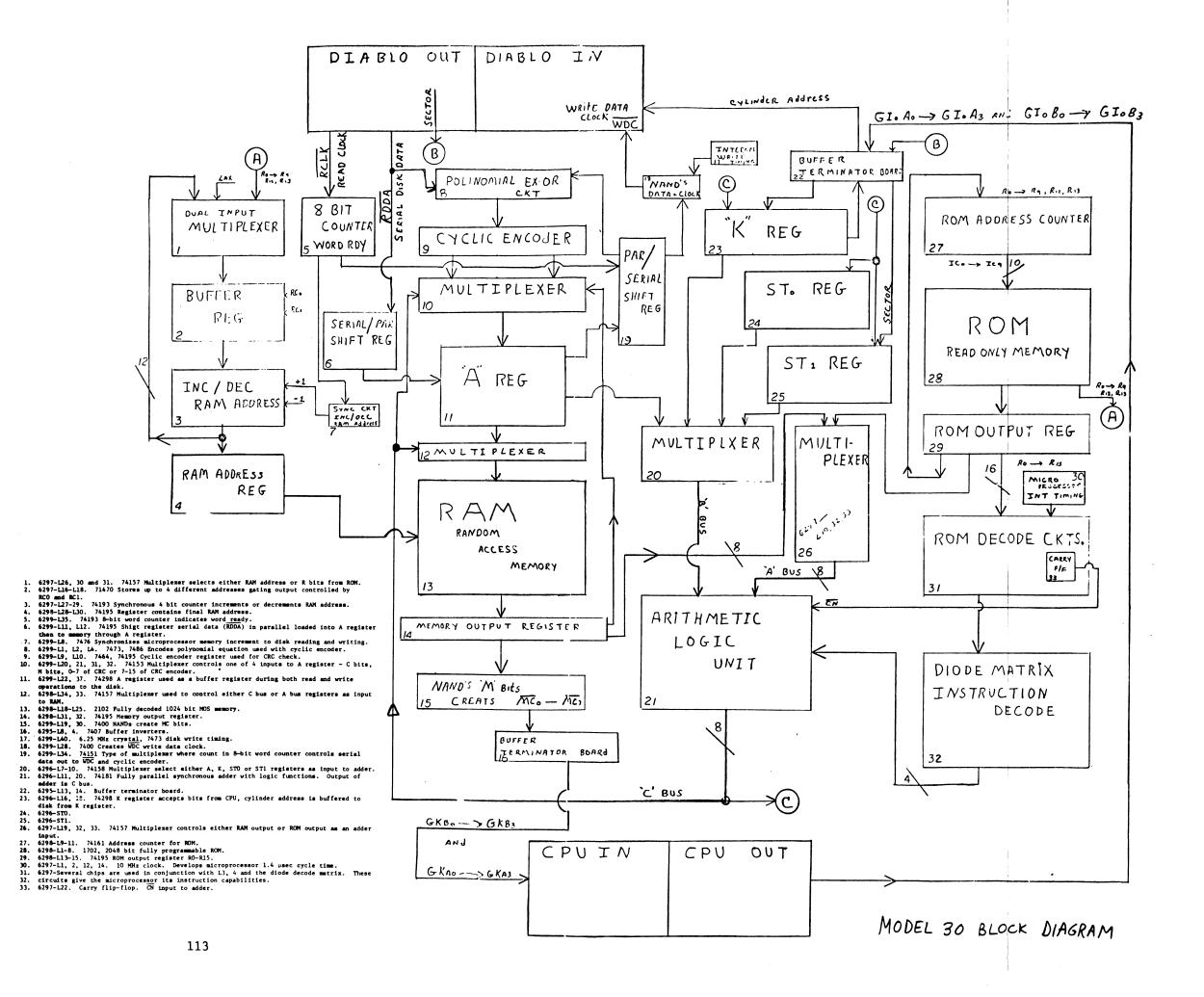

|    | 3 0 MUDI  | ET 20 RIOCE DIACEAM              | 113 |

#### INTRODUCTION

This manual contains technical information concerning the micro-processors of Model 30, 40, 60 and 70 Disk Drives and is to be used as the basic text for future microprocessors. As new microprocessors are designed for new products, addenda to this manual will be published containing the theory of operation of both the software and hardware portions of the new microprocessor.

Presently, October, 1975, the manual consists of Sections 2 and 3. Section 2 is titled the "Model 2270 Microprocessor" and contains descriptions of the basic components of the microprocessor, an explanation of the instruction set (software), a theory of operation (hardware), schematic drawings and a troubleshooting section.

Section 3 contains hardware descriptions of all the boards used in the microprocessors of the 30, 40 and 60 disk drives. This section was written with the assumption that Section 2 has been read.

#### 2. MODEL 2270 MICROPROCESSOR

#### 2.1 MODEL 2270 SIMPLIFIED THEORY OF OPERATION

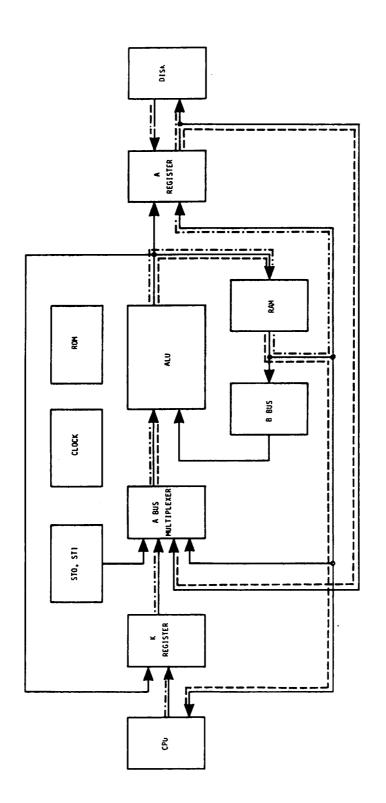

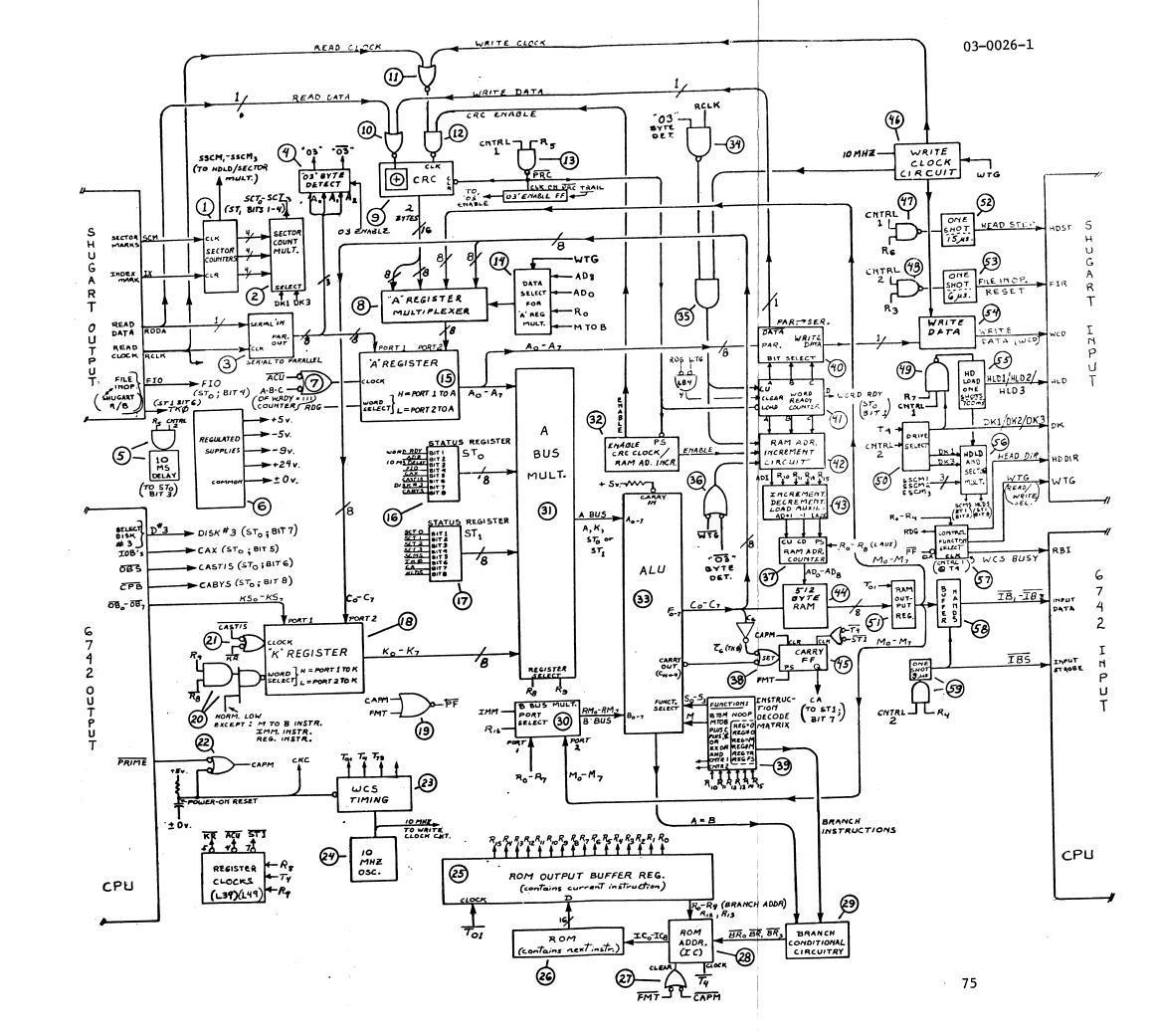

Being similar to most general purpose microprocessors, a typical Wang Labs' disk microprocessor is comprised of the following elements (Refer to Figure 1):

A Read-Only-Memory (ROM); used to control all disk microprocessor operations.

A Random-Access-Memory (RAM); normally used as a transitional working register.

An Arithmetic/Logic Unit (ALU)

Two general purpose registers: The A register, and the K register.

Two Status registers;  $ST_0$  and  $ST_1$ , actually control indicators which sense and set various disk and disk microprocessor conditions.

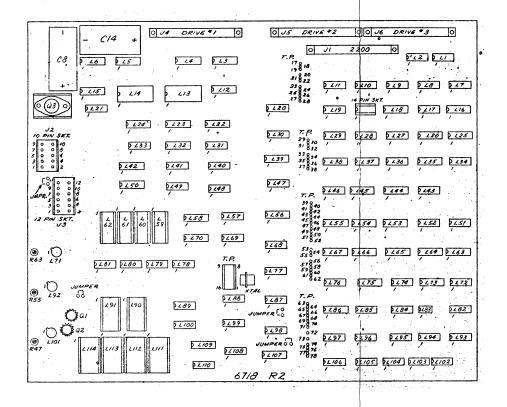

The 6718 or 7018 board contains the entire microprocessor logic for the WCS and Model 2270 disks. Figure 1 shows the simplified block diagram for the 6718/7018 board.

FIGURE 1 SIMPLIFIED BLOCK DIAGRAM

WRITE DATA FLOW

READ DATA FLOW

2

When data is written on the disk (refer to Figure 1), data is strobed into the K register from the CPU and clocked into the A bus multiplexer. The output of the multiplexer is applied to the ALU and sent to the RAM. The RAM outputs the data to the A register which sends the data to be written to the disk.

When data is read from the disk, it is applied to the A register, the A bus multiplexer and on to the ALU. The ALU applies the data to the RAM and finally to the CPU.

The extra lines shown in Figure 1 are not used during a read/write sequence but are used for data manipulation and housekeeping functions before, during and after the read/write sequence.

#### 2.1.1 READ ONLY MEMORY

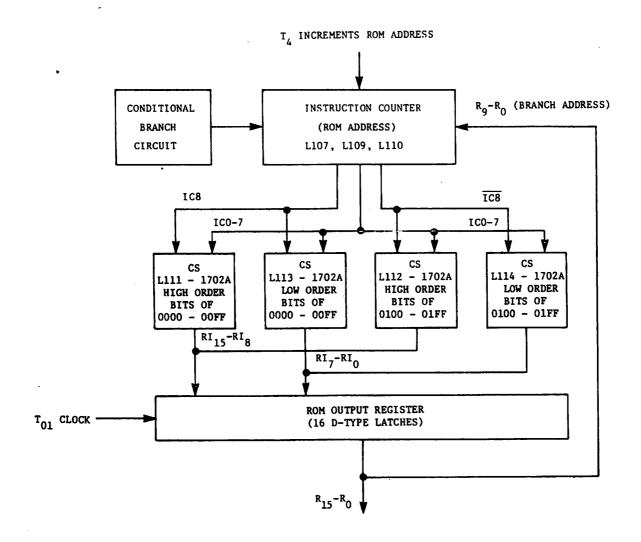

The ROM is the heart of the microprocessor and contains the microprogram for the microprocessor. The 6718 utilizes four INTEL 1702A Programmable Read Only Memory (PROM) Integrated Circuits and the 7018 is capable of using four PROMs or two EA4000 ROM Integrated Circuits. Each PROM contains a 256 x 8 bit matrix and the EA a 512 x 8 matrix.

Since a ROM Instruction requires 16 bits, two PROMs are simultaneously selected to provide a 16 bit output. With this configuration, the total ROM capacity is 512 bytes or steps. See Figure 2.

The steps in the ROM are expressed in hexadecimal notation. Steps  $0000_{16}$  to  $00\mathrm{FF}_{16}$  (0-255) utilize L111 and L113 while steps  $0100_{16}$  to  $01\mathrm{FF}_{16}$  (256-511) utilize L112 and L114. The ROM is addressed by an instruction counter (IC) which normally increments the ROM one step after an instruction has been decoded and performed. Nine bits are applied to the ROM from the IC;  $\mathrm{IC}_{7-0}$  provide the addressing and  $\mathrm{IC}_8$  are used for chip select. The IC can cause the ROM to branch from the increment operation to any address by a branch instruction.

The 16 bit ROM output, RI  $_{15}$  - RI  $_{0}$ , is latched into D-latches and becomes bits R  $_{15}$  - R  $_{0}$ .

FIGURE 2 READ ONLY MEMORY

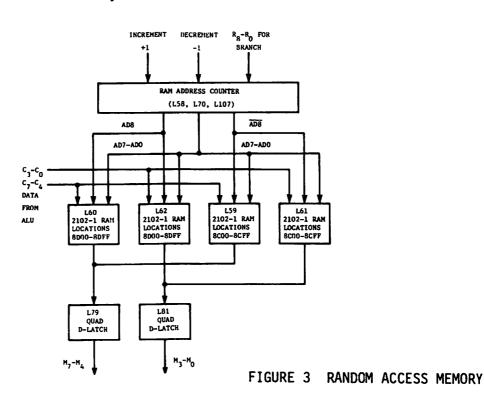

#### 2.1.2 RANDOM ACCESS MEMORY

The RAM consists of four 2101-1 Integrated Circuits with a capacity of 256 x 4 bits resulting in a total storage capacity of 512 bytes. See Figure 3. The RAM address counter addresses the RAM with  $\mathrm{AD_8}$  -  $\mathrm{AD_0}$  bits and can increment, decrement or preset the RAM to any address. Information can only be loaded into the RAM from the ALU,  $\mathrm{C_7}$  -  $\mathrm{C_0}$ , but the output can be transferred to the A register, ALU or the CPU. The ROM is divided into two sections: Locations  $8\mathrm{COO_{16}}$  -  $8\mathrm{CFF_{16}}$  (these are locations 0--255 - the reason for this notation will be explained later) are used for the read/write buffer and various locations between  $8\mathrm{DOO_{16}}$  -  $8\mathrm{DFF_{16}}$  (256-511) are used as a work buffer. Refer to the RAM allocation chart below.

#### RAM ALLOCATION

#### LOCATION

#### DESCRIPTION

| 8C00 |   | SCEE | Read/write buffer                          |

|------|---|------|--------------------------------------------|

| 0000 | _ | ocrr | Read/wille builer                          |

|      |   | 8DOF | Zero sent to the 2200                      |

|      |   | 8D10 | 2200 Address byte #1                       |

|      |   | 8D11 | 2200 Address byte #2                       |

|      |   | 8D12 | 2200 Address byte #3                       |

|      |   | 8D20 | Header byte #1 (track from disk)           |

|      |   | 8D21 | Header byte #2 (sector from disk)          |

|      |   | 8D25 | Disk track #1 (track currently under head) |

|      |   | 8D26 | Disk track #2 (track currently under head) |

|      |   | 8D27 | Disk track #3 (track currently under head) |

|      |   | 8D30 | Error count                                |

|      |   | 8D31 | Internal status                            |

|      |   | 8D32 | Address sent to 2200                       |

|      |   | 8D33 | Format retries                             |

| 8DD4 | _ | 8DE7 | 20 Bytes of zeroes                         |

|      |   | 8DE8 | 03 Byte                                    |

|      |   | 8DE9 | Header byte #1 (track desired)             |

|      |   | 8DEA | Header byte #2 (sector desired)            |

| 8DEB | _ | 8DFE | 20 Bytes of zeroes                         |

|      |   | 8DFF | 03 Byte                                    |

|      |   |      |                                            |

#### 2.1.3 ARITHMETIC/LOGIC UNIT

Two 74181 integrated circuits, designed to perform specific arithmetic or logical operations, as directed by the ROM Microinstruction sequence, comprise the ALU.

This ALU responds to sixteen instructions. Basic ALU inputs consist of the A bus, the B bus, a Carry-In bit, and a function select code decoded from the ROM.

The A bus is the output of a multiplexer, incorporating the A register, the K register, and Status registers  $St_0$  or  $ST_1$  as selectable inputs.

The B bus is the output of a two-part register, incorporating the eight low order ROM bits  $(R_7 - R_0)$ , or the eight bit RAM output  $(M_7 - M_0)$ .

The ALU output is the C bus  $(C_7 - C_0)$ ; data on this bus can be stored in the A register, K register, RAM, or can be transferred to the status registers  $ST_0$  or  $ST_1$ . Again, ALU manipulations are directed by the ROM instruction set.

#### 2.1.4 REGISTER STRUCTURE

#### K Register:

The general purpose K register stores data from either the controlling CPU ( $KS_7 - KS_0$ ), or from the disk microprocessor ALU ( $C_7 - C_0$ ); i.e., whichever source is selected by the ROM for input to the K register.

When commanded by the ROM, the contents of the K register is transferred to the ALU.

#### 2) A Register:

The general purpose A register stores data from (1) the disk microprocessor RAM  $(M_7 - M_0)$ , which is data to be written on the disk, (2) the disk data (a READ), (3) the cyclic redundancy check (CRC) circuitry (verifies disk data accuracy), and (4) the ALU  $(C_7 - C_0)$ . The contents of the A register may be used by the ALU, or may be used as a transitional register for each data byte written on the disk.

#### 3) Status Registers (ST<sub>0</sub>, ST<sub>1</sub>):

Status register ST<sub>0</sub> reports eight disk/CPU conditions to the disk microprocessor, as follows:

Word Ready STO-1 (Bit 1) - The 4th bit of a four-bit binary counter, used to indicate when each byte is ready to be transferred from disk to RAM, via the A register and ALU (WRITE). Word Ready is also used to indicate when each byte is ready to be transferred from RAM to disk via the A register.

Address Bit 8 ST0-2 (Bit 2) - The 9th (highest order) RAM address bit;  $(2^9 = 512 \text{ byte addresses})$ .

10 ms Delay ST0-3 (Bit 3) - The output of an integrated circuit (active for 10 ms). This delay is used to allow time for proper disk access.

File Inoperable STO-4 (Bit 4) - The output of a data safety circuit which indicates when data integrity could be jeopardized by a variety of disk conditions, such as R/W heads not being loaded, drive door open, etc. File Inoperable may be thought of as a Shugart Disk Ready/Not Ready indicator.

CAX STO-5 (Bit 5) - Made up of IOB terms  $IOB_1$  and  $IOB_3$ . CAX distinguishes a select address from a data transfer operation.

Calculator Input Strobe STO-6 (Bit 6) - A strobe from 2200 to disk microprocessor which must accompany each address or data byte from the 2200 to the K register. This status bit indicates that one byte is ready to be transferred from the K register to RAM via the ALU.

Disk #3 STO-7 (Bit 7) - A select line which, when active, indicates that selection of disk #3 is desired.

Calculator Busy STO-8 (Bit 8) - The Ready/Busy indicator from the 2200 CPU I/O controller board.

These bits are sampled by the ALU via the A Bus inputs when ROM bits  $R_9$  and  $R_8 = 10_B$  ( $R_9 = 1$ ;  $R_8 = 0$ ).

Status register  $\operatorname{ST}_1$  reports five disk/disk microprocessor conditions back to the microprocessor as follows:

Sector Bits 0-3 ST1-1 through 4 (Bits 1, 2, 3, 4) - These bits contain the current sector address under the disk drive read/write head. This address is the output of a binary counter, and is monitored as such.

Sector Mark Pulse ST1-5 (Bit 5) - This bit is ultimately the Sector Mark pulse (SCM) from the disk. (One pulse for each sector on the disk). It is used to denote the beginning of each sector.

Track 99 ST1-6 (Bit 6) - A line from the Disk Drive which indicates when the R/W head is positioned at track zero (the outer most track).

Carry ST1-7 (Bit 7) - This is the carry bit for arithmetic operations. It is gated to the ALU for ROM microinstructions specifying carry, and receives that resultant carry.

Head Load ST1-8 (Bit 8) - A signal indicating to the microprocessor that one of the 3 Disk Drive R/W heads have been loaded.

9-

These bits are sampled by the ALU via the B Bus inputs when ROM bits  $R_9$  and  $R_8 = 11_2$ .

#### 2.2 THE INSTRUCTION SET — HARDWARE CONTROL VIA SOFTWARE

#### 2.2.1 GENERAL

Control is implemented via 16-bit ROM instructions, as explained in Section 2.1.1. This 16-bit output (bits  $R_{15}-R_0$ ) is distributed throughout the disk microprocessor, and is subsequently decoded as instructions to perform specific logic operations and data manipulations.

ROM output is formatted such that type of operation, registers involved, destination of resultant data, information source(s), and other control factors are defined by a single 16-bit instruction. The assembled sequence of "microinstructions" is referred to as the microprogram for the peripheral's microprocessor.

There are 24 basic instructions in the 2270 instruction set with each instruction having variables resulting in literally thousands of unique instructions available for data manipulation. The microprocessor hardware is designed so that it can execute every instruction with the end result predictable in every case.

Each of the instructions are comprised of two parts: the operation code and the operand. The operation code is defined as a portion of a computer instruction that indicates which action is to be performed by the computer. ROM bits  $R_{15}$  -  $R_8$  are used as the operation code. Operand is defined as any one of the quantities entering into or arising from an operation. ROM bits  $R_7$  -  $R_0$  comprise the operand.

Operation code bits indicate the following, depending on which instruction category (to be explained later) is applicable:

- 1) Function to be performed.

- 2) Register (A, K,  $ST_0$ ,  $ST_1$ ) used in performing this function.

- 3) Whether to increment/decrement RAM address, or allow current RAM address to remain unchanged.

- 4) Selection of destination for resultant information (function performed). That is, store these results either in a register (A, K, ST<sub>0</sub>, ST<sub>1</sub>) or back into the current RAM location.

- 5) Whether high order bits (7-4) or low order bits (3-0) of the register designated (A, K, ST<sub>0</sub>, ST<sub>1</sub>) will be used for comparisons involved in conditional branch instructions.

Operand code bits indicate the following (again depending on which instruction category is applicable):

- Use operand (via microprocessor ALU B Bus) as mask bits, along with bits (via microprocessor ALU A Bus) from a register (A, K,  $ST_0$ ,  $ST_1$ ) designated by ROM bits  $R_8$  and  $R_9$ .

- 2) Use operand bits  $R_7 R_4$  as a mask for 4-bit Conditional Branch instructions.

- 3) Use operand bits  $R_3 R_0$  or  $R_7 R_0$  as a destination branch address for Conditional Branch instructions.

- 4) Use operand bits  $R_7 R_0$  plus operation code bit  $R_8$  as a destination address for Unconditional Branch instructions.

- 5) Use operand bits  $R_7 R_0$  plus operation code bit  $R_8$  as a new RAM address to be preset via Load Auxiliary instruction in the WCS microprogram.

#### 2.2.2 INSTRUCTION CATEGORIES

The 2270 microprocessor instruction set can be arranged into five major categories.

#### 1) Register Instructions:

An operation using 8 bits of RAM output  $(M_7 - M_0)$  contained at the current RAM address, and 8 bits contained in a register  $(A, K, ST_0, ST_1)$  designated by ROM bits  $R_9$  and  $R_8$ . The results of such instructions are either stored into the current RAM location or stored back into the register designated by ROM bits  $R_9$  and  $R_8$ . The RAM address can be incremented, decremented or remain unchanged by bits  $R_{11}$  and  $R_{10}$ .

There are eight register instructions as explained below:

#### INSTRUCTION

#### **EXPLANATION**

NOOP

No operation. Used as a filler command and has no effect but to cause the ROM address to increment.

B to M

B to memory. Transfers contents of B (buffer register A, K, STØ or ST1) to memory and causes RAM address to increment, decrement or remain unchanged.

M to B

Memory to B. Transfers contents of memory to B (buffer register A, K, STØ or ST1) and causes RAM address to increment, decrement or remain unchanged.

Add wo/carry

Binary add without carry bit. A binary add of the contents of B (buffer register A, K, STØ or ST1) and RAM with result to RAM or B and causes RAM address to increment, decrement or remain unchanged.

OR

Logical OR function. ORs the contents of B (buffer register A, K, STØ or ST1) with RAM with result to RAM or B and causes RAM address to increment, decrement or remain unchanged.

XOR

Exclusive OR function. Same as OR function except contents of B and RAM are exclusive ORed.

Add w/carry

Binary add with carry bit. Same as add without carry instruction.

AND

Logical AND function. ANDs the contents of B (buffer register A, K, STØ or ST1) with contents of RAM with result to RAM or B and causes RAM address to increment, decrement or remain unchanged.

#### 2) Immediate Instructions:

An operation using 8 bits of ROM output  $(R_7-R_0)$  contained at the current ROM address, and 8 bits contained in a register (A, K, ST<sub>0</sub>, ST<sub>1</sub>) designated by ROM bits  $R_8$  and  $R_9$ . The results of such instructions are stored back into the designated register  $(R_8, R_9)$ .

There are four immediate instructions as explained below:

#### INSTRUCTION

#### **EXPLANATION**

OR Immediate

Logical OR function. The contents of a register (A, K, STØ or ST1) are ORed with the eight least significant bits of ROM with the result stored back into the register.

XOR Immediate

Exclusive OR function. Same as OR Immediate except contents are exclusive ORed.

Add w/carry Imm.

Binary add with carry bit. The binary add w/carry bit of a register (A, K, STØ or ST1) with the eight least significant bits of ROM with the result stored back into the register.

AND Immediate Logical AND function. Same as OR Immediate except contents are ANDed.

#### 3) Branch Instructions:

These instructions are divided into two categories: conditional branch and unconditional branch. The conditional branch instructions allow from 0 to  $\pm$  15 microprogram step jumps; or, from 0 to  $\pm$  255 microprogram step jumps (depending on which conditional branch instruction is performed). The unconditional branch instructions causes a jump to any step within the microprocessor's microprogram.

There are eight branch instructions as explained below:

#### INSTRUCTION

#### EXPLANATION

Br if Reg. = 0 Branch if register = 0. Conditional branch to step indicated by the eight least significant bits of ROM if register (A, K, STØ or ST1) equals zero. Maximum number of steps is +255.

Br. if Reg. \( \nabla \) Branch if register \( \nabla \) 0. Same as above if register does not equal zero.

Br. if True L,H Branch if True Low or Branch if True High. Conditional branch to step indicated by ROM bits  $R_3 - R_0$  if the 4 least significant bits (Low) or the 4 most significant bits (High) of register (A, K, STØ or ST1) equal any corresponding true ROM bits  $R_7 - R_4$ . Maximum number of branch steps is  $\pm 15$ .

Br. if False L,H Branch if False Low or Branch if False High. Conditional branch to step indicated by ROM bits  $R_3$  -  $R_0$  if the 4 LSB (Low) or the 4 MSB (High) of register (A, K, STØ or ST1) equal any corresponding false ROM bits  $R_7$  -  $R_4$ . Maximum number of branch steps is  $\pm 15$ .

Br. if = Mask Branch if equal to Mask. Conditional branch to step indicated by ROM bits  $R_3 - R_0$  if either the 4 LSB or 4 MSB (selected by a bit of the instruction code) of a register (A, K, STØ or ST1) equal the mask of ROM bits  $R_7 - R_A$ . Maximum # of branch steps is  $\pm 15$ .

Br. if # Mask Branch if not equal to Mask. Same as above if register does not equal mask.

UB to steps 0-255 Unconditional Branch to steps 0-255. In the form of HEX 88YY, causes the microprogram to branch to the address contained in YY to one of the first 256 steps of the microprogram (steps 0-255).

UB to steps 256-511 Unconditional Branch to steps 256-511. In the form of HEX 89YY, causes the microprogram to branch to the address contained in YY to one of the second 256 steps of the microprogram (steps 256-511).

#### 4) RAM Address Instructions:

These two instructions allow the ROM outputs  $R_8 - R_0$  to preset the RAM address.

#### INSTRUCTION

#### **EXPLANATION**

Load Aux. (0-255) Load Auxiliary. Enables the ROM bits  $R_8-R_0$  to preset the RAM to any address between 0-255 (the data buffer). The instruction takes the form of HEX 8CXX where XX is the RAM address.

Load Aux. (256-511) Load Auxiliary. Enables the ROM bits  $R_8$  -  $R_0$  to preset the RAM to any address between 256 and 511 (the work buffer). The instruction takes the form of 8DXX where XX is the RAM address.

#### 5) Control Instructions:

Control instructions initiate disk functions such as disk head movement, read, write, format, etc. These instructions are decoded directly from ROM outputs to peripheral interfacing hardware in the microprocessor. The ALU is not involved in these instructions.

There are 14 control functions used in the 2270:

#### INSTRUCTION

#### **EXPLANATION**

Control 1 Takes the form of HEX ECXX where

ECO1 - Turn on read gate (RDG)

ECO2 - Turn on write gate (WTG)

ECO4 - Turn on busy signal (BSY)

EC08 - Format (FMT)

EC10 - Head direction Select (HD DIR)

EC20 - Preset CRC (PRC)

EC40 - Head step (HD ST)

EC80 - Head load (HD LD)

#### Control 2

Takes the form of HEX FCXX where

FC01 - Select drive #3

FCO2 - Select drive #2

FC04 - Select drive #1

FC08 - Clear file inop. (FIR)

FC10 - Strobe to 2200

FC20 - 10 ms delay

FC40 - Not used

FC80 - Not used

#### 2.2.3 INSTRUCTION SET SUMMARY

#### 2.2.3.1 Introduction

Tables 1, 2 and 3 summarize the 24 instructions. Table 1 lists all the instructions and is divided into three major columns. The first

column labeled "instruction category" contains the instruction names arranged by category as explained in Section 2.2.2. The second major column is labeled "operation code bits" and lists in binary the eight most significant bits of ROM output. This is the first half of any instruction, the operation code. The third major column is labeled "operand code bits" and lists in binary the eight least significant bits of ROM output. This is the second half of any instruction, the operand.

Referring to the second major column, it is noted that ROM bits  $R_{15}^{-R}$  are fixed ones and zeroes for the register instructions but that bits  $R_{11}^{-R}$  may vary. The I/D heading under ROM bits  $R_{11}$  and  $R_{10}$  indicates increment or decrement of RAM address depending upon the status of these two bits.

It is at this point that Table 2 is required; Table 2 is an expansion of all the abbreviations used in Table 1. Referring to Table 2, the I/D bits are expanded into the four possible configurations. For example, if I/D bits  $R_{11}$  and  $R_{10}$  are a one and zero respectively for a register instruction, the result of the operation is stored in RAM and the RAM address is decremented one location.

Again referring back to Table 1, the last two bits of the operation code (bits  $R_9$  and  $R_8$ ) determine what register is to be used in the operation. This column is headed by "REG." which is an abbreviation for register. Observing Table 2, the two bits decode one of the four registers. For example, if ROM bits  $R_9$  and  $R_8$  are both low during a register instruction, the A register is the selected register.

Table 3 allows the reader to disregard Tables 1 and 2 since Table 3 is a breakdown of all the instructions in hexadecimal form. For example, if a  $1700_{16}$  code is encountered in the program, the reader would be forced to convert the hexadecimal code to binary (0001011100000000), refer to Table 1 for the type of instruction, and finally to Table 2 to determine the register used and whether or not the RAM address is incremented or decremented. However, by utilizing Table 3, the reader can instantly determine that a  $1700_{16}$  code is a B to M instruction involving register ST1 and incrementing the RAM address.

TABLE 1

2270 MICROPROCESSOR INSTRUCTION SET

|                                                                                                   | OI                  | PER              | ATI                   | ON               | CODE                       | BITS                    | -(R <sub>15</sub> -   | ·R <sub>8</sub> ) | OPERAND CODE BITS-(R <sub>7</sub> -R <sub>0</sub> )                              |  |  |  |

|---------------------------------------------------------------------------------------------------|---------------------|------------------|-----------------------|------------------|----------------------------|-------------------------|-----------------------|-------------------|----------------------------------------------------------------------------------|--|--|--|

| INSTRUCTION CATEGORY                                                                              | 15 1                | L4               | 13                    | 12               | 11                         | 10                      | 9                     | 8                 | 7 6 5 4 3 2 1 0                                                                  |  |  |  |

| REGISTER INSTRUCTIONS                                                                             | INST                | CRUC             |                       | NC               | I/D                        |                         | REG.                  |                   | OPERAND                                                                          |  |  |  |

| NO-OP B to Memory Memory to B Binary ADD wo/carry OR XOR - Exclusive OR Binary ADD with carry AND | 0<br>0<br>0         | 0<br>0<br>0<br>1 | 0<br>1<br>1<br>0<br>0 | 1<br>0<br>1<br>0 | ID ID ID ID ID ID ID ID ID | ID ID ID ID ID ID ID ID | B<br>B<br>B<br>B<br>B |                   | Not Used<br>Not Used<br>Not Used<br>Not Used<br>Not Used<br>Not Used<br>Not Used |  |  |  |

| IMMEDIATE INSTRUCTIONS                                                                            | INST                | ru               | CTI                   | ON               | CODE                       |                         | REG.                  | ,                 | IMMEDIATE OPERAND (B BUS)                                                        |  |  |  |

| OR Immediate XOR Immediate Binary ADD w/carry Immed AND Immediate                                 | 1                   | 1                | 0<br>0<br>1<br>1      | 1<br>0           | 1<br>1                     | 0<br>0<br>0<br>0        | В<br>В<br>В           |                   | I I I I I I I I I I I I I I I I I I I                                            |  |  |  |

| BRANCH INSTRUCTIONS (Conditional; 8 bit)                                                          | INSTRUCTION CODE RE |                  |                       |                  |                            |                         |                       |                   | BRANCH ADDRESS (B BUS)                                                           |  |  |  |

| Branch if Register = 0 Branch if Register ≠ 0                                                     | 1<br>1              | 1                | 0                     | 0                | 1                          | 1                       | B<br>B                |                   | Y Y Y Y Y Y Y<br>Y Y Y Y Y Y Y                                                   |  |  |  |

| MASK BRANCH INSTRUCTIONS (Conditional; 4 bit)                                                     | INS                 | TRU              | СТІ                   | ON               | CODE                       | H/L                     | REG.                  | •                 | MASK BRANCH ADDRESS                                                              |  |  |  |

| Branch IF True<br>Branch IF False<br>Branch IF = Mask<br>Branch IF ≠ Mask                         | 1                   | 0                |                       | 1                | 0<br>0                     | S<br>S<br>S             | B<br>B<br>B           |                   | M M M M Y Y Y Y<br>M M M M Y Y Y Y<br>M M M M                                    |  |  |  |

| UNCONDITIONAL BRANCH                                                                              | INS'                | TRU              | CTI                   | ON               | CODE                       |                         |                       |                   | BRANCH ADDRESS                                                                   |  |  |  |

| TO STEPS 0-255<br>(0000-00FF)<br>TO STEPS 256-511<br>(0100-01FF)                                  |                     |                  | 0                     |                  | 1                          | 0                       | 0                     | 0                 | Y Y Y Y Y Y Y<br>Y Y Y Y Y Y Y                                                   |  |  |  |

| RAM ADDRESS INSTRUCTIONS                                                                          | INS                 | TRU              | CTI                   | ON               | CODE                       |                         |                       |                   | RAM ADDRESS LOADED                                                               |  |  |  |

| LOAD AUX<br>(DATA BUFFER)<br>LOAD AUX<br>(WORK BUFFER)                                            |                     |                  |                       |                  | 1                          | 1                       | 0                     | 0                 | x x x x x x x x x                                                                |  |  |  |

| CONTROL INSTRUCTIONS                                                                              | INSTRUCTION CODE    |                  |                       |                  |                            |                         |                       |                   | CONTROL OPERAND                                                                  |  |  |  |

| Control 1<br>Control 2                                                                            |                     |                  |                       |                  | 1                          |                         | 0                     | 0                 | 2                                                                                |  |  |  |

#### TABLE 2

### EXPLANATION OF LETTER DESIGNATIONS FOR INSTRUCTION SET BITS

- I/D = Increment/decrement of RAM Address

- 00 = Result to original RAM address; no increment

or decrement

- 01 = Result to original RAM address then

increment (+1)

- 10 = Result to original RAM address then

decrement (-1)

- 11 = Result to selected register(B) and increment

RAM address

REG. = Selected register

$I = Immediate Operand (R_0 - R_7 Mask)$

00 = A register

01 = K register

M = Mask; a unique configuration of binary bits.

10 = Status Reg. 0

11 = Status Reg. 1

Y = Branch Address

- S = High order or Low order 4-bits for MASK Branch Instruction.

- 0 = Low order (Bits 0 3)

- l = High order (Bits 4 7)

- X = New R. A. M. Address for LOAD Aux

- Z = Control Operand

Control 1 (ECZZ<sub>16</sub>):

- ECO1 Turn on Read Gate; RDG (CNTRL1 AND R<sub>O</sub>)

- ECO2 Turn on Write Gate; WTG (CNTRL1 AND  $\rm R_1$ )

- ECO4 Turn on Busy Signal; BSY (CNTRL1 AND R<sub>2</sub>)

- EC08 Not used (CNTRL1 AND  $R_3$ )

- EC10 Head Direction Select; HD DIR (CNTRL1 AND  $R_{\lambda}$ )

- EC20 PRC (CNTRL1 AND  $R_5$ )

- EC40 Head Step; HD ST (CNTRL1 AND  $R_6$ )

- EC80 Head Load; HD LD (CNTRL1 AND R<sub>7</sub>)

Control 2 (FCZZ<sub>16</sub>)

FCO1 - Select Drive #3 - (CNTRL2 AND  $R_0$ )

FCO2 - Select Drive #2 - (CNTRL2 AND R<sub>1</sub>)

FCO4 - Select Drive #1 - (CNTRL2 AND  $R_2$ )

FCO8 - Clear File Inop.; FIR - (CNTRL2 AND  $R_3$ )

FC10 - Strobe to 2200 - (CNTRL2 AND  $R_4$ )

FC20 - 10 ms. Delay - (CNTRL2 AND  $R_5$ )

FC40 - Not used - (CNTRL2 AND  $R_6$ )

FC80 - Not used - (CNTRL2 AND R<sub>7</sub>)

## TABLE 3 EXPANDED BREAKDOWN OF MICROPROCESSOR OPERATION CODES

#### B To M

| 1. | A    | K    | St0  | Stl  |            |

|----|------|------|------|------|------------|

|    | 1000 | 1100 | 1200 | 1300 | No RAM I/D |

|    | 1400 | 1500 | 1600 | 1700 | AD + 1     |

|    | 1800 | 1900 | 1A00 | 1800 | AD - 1     |

#### M To B

| 2. | Α    | K    | St0  | St1  |            |

|----|------|------|------|------|------------|

|    | 2000 | 2100 | 2200 | 2300 | No RAM I/D |

|    | 2400 | 2500 | 2600 | 2700 | AD + 1     |

|    | 2800 | 2900 | 2A00 | 2B00 | AD - 1     |

#### Add Without Carry (RAM)

| 3. | A    | K    | StO  | St1  |                    |

|----|------|------|------|------|--------------------|

|    | 3000 | 3100 | 3200 | 3300 | No RAM I/D         |

|    | 3400 | 3500 | 3600 | 3700 | AD + 1             |

|    | 3800 | 3900 | 3A00 | 3B00 | AD - 1             |

|    | 3C00 | 3D00 | 3E00 | 3F00 | AD + 1 Result to B |

#### OR (RAM)

| 4. | A    | K          | StO      | Stl           |                    |

|----|------|------------|----------|---------------|--------------------|

|    | 4000 | 4100       | 4200     | 4300          | No RAM I/D         |

|    | 4400 | 4500       | 4600     | 4700          | AD + 1             |

|    | 4800 | 4900       | 4A00     | 4B00          | AD - 1             |

|    | 4C00 | 4D00       | 4E00     | 4F00          | AD + 1 Result to B |

|    |      |            | Exclusiv | ve OR (RAI    | M)                 |

| 5. | A    | K          | St0      | St1           |                    |

|    | 5000 | 5100       | 5200     | 5300          | No RAM I/D         |

|    | 5400 | 5500       | 5600     | 5700          | AD + 1             |

|    | 5800 | 5900       | 5A00     | 5B00          | AD - 1             |

|    | 5C00 | 5D00       | 5E00     | 5F00          | AD + 1 Result to B |

|    |      |            | Add With | Carry (R      | AM)                |

| 6. | A    | K          | St0      | St1           |                    |

|    | 6000 | 6100       | 6200     | 6300          | No RAM I/D         |

|    | 6400 | 6500       | 6600     | 6700          | AD + 1             |

|    | 6800 | 6900       | 6A00     | 6B00          | AD - 1             |

|    | 6C00 | 6D00       | 6E00     | 6 <b>F</b> 00 | AD + 1 Result to B |

|    |      |            | AN       | D (RAM)       |                    |

| 7. | A    | · <b>K</b> | St0      | St1           |                    |

|    | 7000 | 7100       | 7200     | 7300          | No RAM I/D         |

|    | 7400 | 7500       | 7600     | 7700          | AD + 1             |

|    | 7800 | 7900       | 7A00     | 7B00          | AD - 1             |

|    | 7C00 | 7D00       | 7E00     | 7F00          | AD + 1 Result to B |

| 8. |      | OR Imm     | ediate   |               |                    |

| J. | C8II | C9II       | CAII     | CBII          |                    |

9. Exclusive OR Immediate

D8II D9II DAII DBII

10. Add With Carry Immediate

E8II E9II EAII EBII

11. AND Immediate

**;**

F8II F9II FAII FBII

#### Branch Commands

- 12. Α K St0 St1 80MY 81MY 82MY 83MY = Mask L = Mask H **'84MY** 85MY 86MY 87MY 92MY # Mask L 90MY 91MY 93MY ≠ Mask H Can only branch 95MY 96MY 97MY **94MY** A1MY A2MY A3MY True L within a +15 step **AOMY** A4MY A5MY A6MY A7MY True H area. B2MY B3MY False L **BOMY** BLMY False H B5MY B6MY B7MY **B4MY** = 0Can branch within CEYY **CFYY** CCYY **CDYY #** 0 a +255 step area. DCYY **DDYY** DEYY DFYY

- 13. Unconditional Branch = 88YY steps 0 255 in microprogram

89YY steps 256-511 in microprogram

- 14. Load Auxiliary = 8CXX RAM 0 255 (DATA BUFFER) 8DXX - RAM 256-511 (WORK BUFFER)

- 15. Control 1 = ECZZ (See Table 2)

Control 2 = FCZZ (See Table 2)

#### 2.2.3.2 Instruction Set Examples

#### 1) Register Instructions

The following two examples are typical of Register Instruction decoding:

EXAMPLE: 10XX<sub>16</sub> (B to M)

Binary Value

|   |                 | HE              | X 1             |                 |                 | HE              | к о            |                |                | n              | /a             |                |                | n              | /a             |                |

|---|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| : | 0               | 0               | 0               | 1               | 0               | 0               | 0              | 0              | X              | X              | Х              | X              | X              | X              | Х              | X              |

|   | R <sub>15</sub> | R <sub>14</sub> | R <sub>13</sub> | R <sub>12</sub> | R <sub>11</sub> | R <sub>10</sub> | R <sub>9</sub> | R <sub>8</sub> | R <sub>7</sub> | R <sub>6</sub> | R <sub>5</sub> | R <sub>4</sub> | R <sub>3</sub> | R <sub>2</sub> | R <sub>1</sub> | R <sub>O</sub> |

Where: 0 = low (+0V)

1 = high (+5V)

X = don't care

In the above register instruction,  $R_{15}-R_{12}$  identify a Register-to-Memory command (sometimes referred to as B-to-M, in notation form). ROM bits  $R_{11}$  and  $R_{10}$  indicate that RAM address will not be incremented and that the contents of the A register (designated by ROM bits  $R_{9,8}=00_2$ ) will be stored at the current RAM location. ROM bits  $R_7-R_0$  are not used in register instructions. The above information can be verified by using Tables 1 and 2. However, by referring to Table 3, the  $10XX_{16}$  code is immediately recognized as a B to M with the A register and no RAM increment or decrement.

EXAMPLE: 65XX<sub>16</sub> (Add with Carry)

Binary Value

|                 | HE              | X 6             |                 |                 | HE              | X 5            |                |                | n              | /a             |                |                | n              | /a             |            |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|------------|

| 0               | 1               | 1               | 0               | 0               | 1               | 0              | 1              | Х              | X              | X              | X              | Х              | Х              | Х              | Х          |

| R <sub>15</sub> | R <sub>14</sub> | R <sub>13</sub> | R <sub>12</sub> | R <sub>11</sub> | R <sub>10</sub> | R <sub>9</sub> | R <sub>8</sub> | R <sub>7</sub> | R <sub>6</sub> | R <sub>5</sub> | R <sub>4</sub> | R <sub>3</sub> | R <sub>2</sub> | <sup>R</sup> 1 | $^{R}_{0}$ |

For this instruction,  $R_{15} - R_{12}$  designate that a Binary Add with Carry will be performed between the 8 bits at the current RAM location, and the 8-bit contents of the register designated by ROM bits  $R_9$ ,  $R_8$ . In this case,  $R_9$  and  $R_8 = 01_2$ , designating

the 8-bit K register. The Binary Add with Carry is performed, and  $R_{11}$  and  $R_{10}$  indicate that the result is stored at the current RAM location and then the RAM address is incremented. Referring to Table 3, the 65XX code is decoded as an Add with Carry instruction involving the K register and incrementing the RAM address.

Generally speaking, a Register instruction is an operation performed between an eight bit register  $(A, K, ST_0, ST_1)$  designated by  $R_9$ ,  $R_8$  and the eight bits stored at the current RAM address.

#### 2) Immediate Instructions

The following example is typical of Immediate Instruction decoding:

EXAMPLE: F8AA<sub>16</sub> (AND Immediate)

|              |                 | HEX             | K F             |                 |                 | НЕХ             | ٤ 3            |                |                | HE             | X A            |                |                | HE             | X A            |                |

|--------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| Binary Value | 1               | 1               | 1               | 1               | 1               | 0               | 0              | 0              | 1              | 0              | 1              | 0              | 1              | 0              | 1              | 0              |

|              | R <sub>15</sub> | R <sub>14</sub> | R <sub>13</sub> | R <sub>12</sub> | R <sub>11</sub> | R <sub>10</sub> | R <sub>9</sub> | R <sub>8</sub> | R <sub>7</sub> | R <sub>6</sub> | R <sub>5</sub> | R <sub>4</sub> | R <sub>3</sub> | R <sub>2</sub> | R <sub>1</sub> | R <sub>O</sub> |

All Immediate Instructions are performed using the 8 bits contained in a register (A, K,  $ST_0$ ,  $ST_1$ ) designated by  $R_9$  and  $R_8$ , and the 8-bit mask presented in  $R_7$  -  $R_0$ . The results of Immediate Instructions are transferred back to the designated register (A, K,  $ST_0$ ,  $ST_1$ ).

For the example Immediate Instruction F8AA, ROM bits  $R_{15} - R_{10}$  designate an AND IMMEDIATE operation. The result of this AND IMMEDIATE is stored back into designated register A  $(R_9, R_8 = 00_2)$ . This can be verified by using Table 3.

The 8-bit mask present in bits  $R_7 - R_0$  (10101010) are the bits that are ANDed in the ALU with the present contents of RAM.

As an example, if the RAM contains a bit configuration of 11110000 and this AND Immediate is executed, the final result in the A register would be a bit configuration of 10100000 (10101010 ANDed with 11110000 = 10100000).

#### 3) Branch Instructions

The various Branch instructions are explained individually:

First, there are eight 4-bit Branch instructions; they cause a branch from 0 to  $\pm$  15 steps from the current microprogram step if a specified condition is met. These eight 4-bit instructions belong to the *conditional* category of Branch instructions.

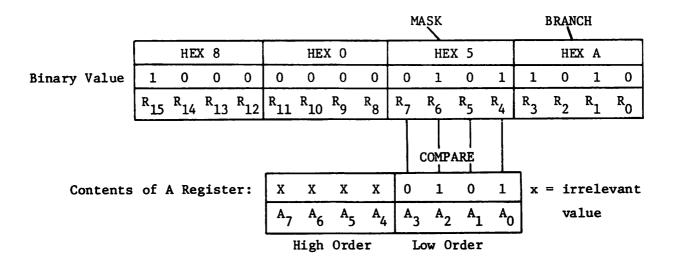

3

Four ROM bits  $(R_3 - R_0)$  determine the Branch address; therefore, there are 16  $(2^4)$  unique combinations of those binary bits possible. Thus (for example) if the current ROM address is  $0000_{16}$ , and the Branch address specified by  $R_3 - R_0$  is  $1111_2$ , a jump of +15 steps is performed, branching the microprogram to ROM address  $000F_{16}$ . Conversely, if the current ROM address is  $000F_{16}$ , and the Branch address specified by  $R_3 - R_0$  is  $0000_2$ , a jump of -15 steps is performed, branching the microprogram to ROM address  $0000_{16}$ . These 4-bit conditional branch instructions compare the contents of a register designated by  $R_9$  and  $R_8$  to a mask presented by bits  $R_7 - R_4$ . If the conditions of the branch are met, branch to a step (ROM address) designated by  $R_3 - R_0$  is made. If the conditions of the branch are not met, the microprogram continues sequentially to the next step in that routine.

Since these instructions can only compare four bits of a register specified by  $R_9$  and  $R_8$  with the four mask bits  $(R_7-R_4)$ , either the four high order bits or the four low order bits of the designated register is specified by ROM bit  $R_{10}$ . If  $R_{10}$  = high, or logical "one", compare bits 7-4 of the designated register with mask bits  $R_7$  -  $R_4$ ; if  $R_{10}$  = low, or logical "zero", compare bits 3-0 of the designated register with mask bits  $R_7$  -  $R_4$ .

The following examples are typical of each four bit conditional branch instruction.

EXAMPLE:  $805A_{16}$  (Br A = ML)

This instruction causes a branch by changing the current set up of  $IC_7 - IC_0$ . Actually, the only bits of ROM address that change from the current address are  $IC_{0-3}$ . This ROM address modification takes place only if the *low* order bits of the A register  $(A_3 - A_0)$  are identical to the mask presented in  $R_7 - R_4$ . With the A register in the state indicated above, the condition sought is met and a branch is performed.

If the current ROM step (address) was:

The new address would be:

Since the new address =  $010_{10}$  (= $A_{16}$ ) And the previous address =  $07_{10}$  (= $7_{16}$ )

Subtract -

Branch to address 0A (a jump of +3) occurs when specified conditions are met.

The above example microinstruction, 805A, is a typical "Branch if A = Mask Low" conditional branch in the microprocessor.

EXAMPLE:  $8426_{16}$  (Br. A = MH)

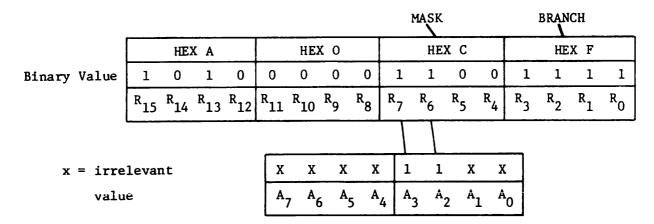

MASK **BRANCH** HEX 4 HEX 2 HEX 8 HEX 6 Binary Value 0 0 0 1 1 1 0 COMPARE x = irrelevant Contents of A register: X X X X value

This instruction causes a branch to the ROM address designated by  $R_3 - R_0$  if the *high* order bits of the A register  $(A_7 - A_4)$  are equal to the mask presented in  $R_7 - R_4$ . Again, the specified condition is met and the branch is performed. The ROM address is changed in the same manner as the previous  $805A_{16}$  example.

The example microinstruction 8426 is a typical 'Branch if = Mask High' conditional branch in the microprocessor.

EXAMPLE:  $AOCF_{16}$  (Br A = TL)

This instruction causes a branch only if the configuration of TRUE (ON; logic '1') bits presented in the  $\rm R_7$  -  $\rm R_4$  mask match the configuration of TRUE (ON; logic '1'; high) bits contained in the four low order bits (3-0) of a register designated by ROM bits  $\rm R_8$  and  $\rm R_9$ . ROM bits  $\rm R_{15}$  -  $\rm R_{11}$  designate Branch if True; bit  $\rm R_{10}$  (=0) designates four low order bits of the register selected by  $\rm R_8$  and  $\rm R_9$ , which in this case is the A register.

Generally speaking, this is called a Branch if True Low (Branch if A register low order TRUE bits match  $R_7 - R_4$  TRUE bits). If any one of the TRUE mask bits  $R_7 - R_4$  do not match up to a corresponding true bit in  $A_3 - A_0$ , no branch occurs.

ROM address is modified for branch in the same manner as the previous  $805A_{16}$  example.

Since only TRUE mask bits are being compared, any other TRUE bits in the selected register not corresponding to TRUE bits in the mask are ignored.

If "Branch IF True High" is the instruction, the four high order bits of the A register would be used to compare with the TRUE mask bits presented in  $R_7$  -  $R_4$ .

EXAMPLE:  $B03F_{16}$  (A = FL)

| -        |                 |                 |                 |                 |                 |                 |                |                | 1              | MASK           |                |                | BRANCH         |                |                |                |

|----------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

|          |                 | HE              | ХВ              |                 | HEX O           |                 |                |                |                | HE             | х 3            |                | HEX F          |                |                |                |

|          | 1               | 0               | 1               | 1               | 0               | 0               | 0              | 0              | 0              | 0              | 1              | 1              | 1              | 1              | 1              | 1              |

|          | R <sub>15</sub> | R <sub>14</sub> | R <sub>13</sub> | R <sub>12</sub> | R <sub>11</sub> | R <sub>10</sub> | R <sub>9</sub> | R <sub>8</sub> | R <sub>7</sub> | R <sub>6</sub> | R <sub>5</sub> | R <sub>4</sub> | R <sub>3</sub> | R <sub>2</sub> | R <sub>1</sub> | R <sub>0</sub> |

| Contents | of A            | A Reg           | giste           | er: [           | х               | Х               | х              | х              | 0              | <i>I</i>       | х              | х              | ]              | X =            | irre           | levan          |

|          |                 |                 |                 |                 | A <sub>7</sub>  | <sup>A</sup> 6  | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |                |                | val            | ue             |

This instruction causes a branch if the configuration of false (low; 0) bits presented in the  $R_7$  -  $R_4$  FALSE mask bits (bits  $R_7$  and  $R_6$  in this case) match up to corresponding low order FALSE bits in the A register (A<sub>3</sub> and A<sub>2</sub> in this case).

A "Branch IF False High" instruction follows the same format as the above example. The only difference being that the FALSE high order bits of the selected register (the A register in this example) would be compared.

The two remaining conditional branch instructions have the capability to branch 0 to  $\pm$  255 steps from the current step in the microprogram. This is achieved by changing IC $_7$  - IC $_0$ . Unlike the 4 bit conditional branch instructions which actually can modify only the four low order ROM address bits (IC $_3$  - IC $_0$ ), all 8 ROM address bits can be changed to the address contained in bits R $_7$  - R $_0$ . These instructions cause a branch only if all eight bits of the register designated by R $_9$  and R $_8$  are either =0 or  $\neq 0$ .

These two instructions are as follows:

BRANCH IF REGISTER =0: 1 1 0 0 1 B B Y Y Y Y Y Y Y Y BRANCH IF REGISTER  $\neq 0$ : 1 1 0 1 1 B B Y Y Y Y Y Y Y Y Where B = selected register

EXAMPLE: DD2C<sub>16</sub> (Branch IF Reg  $\neq$  0)

|                 | HE              | K D             |                 |                 | HE              | X D            |                |                | Н              | EX 2           |                | нех с          |                |                |                |  |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|--|

| 1               | 1               | 0               | 1               | 1               | 1               | 0              | 1              | 0              | 0              | 1              | 0              | 1              | 1              | 0              | 0              |  |

| R <sub>15</sub> | R <sub>14</sub> | R <sub>13</sub> | R <sub>12</sub> | R <sub>11</sub> | R <sub>10</sub> | R <sub>9</sub> | R <sub>8</sub> | R <sub>7</sub> | R <sub>6</sub> | R <sub>5</sub> | R <sub>4</sub> | R <sub>3</sub> | R <sub>2</sub> | R <sub>1</sub> | R <sub>O</sub> |  |

The example causes a branch from the current step, to step 002C or 012C, (depending on whether the current step lies within steps 0000 - 00FF or within 0100 - 01FF) if register K ('B' = 01) is any value other than zero.

The last Branch Instruction category is the *Unconditional* Branch. These instructions cause a direct branch to any step in the microprogram, subject to no conditions.

These two instructions are as follows:

#### UNCONDITIONAL BRANCH 88YY

(to 0000 thru 00FF) 1 0 0 0 1 0 0 0 Y Y Y Y Y Y Y Y

#### UNCONDITIONAL BRANCH 89YY

(to 0100 thru 01FF) 1 0 0 0 1 0 0 1 Y Y Y Y Y Y Y Y

EXAMPLE: 89 C5<sub>16</sub> (UB)

|                 | HEX             | K 8             |                 |                 | HE              | K 9            |                | HEX C HEX      |                |                |                |                | EX 5           | 5              |                |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| 1               | 0               | 0               | 0               | 1               | 0               | 0              | 1              | 1              | 1              | 0              | 0              | 0              | 1              | 0              | 1              |

| R <sub>15</sub> | R <sub>14</sub> | R <sub>13</sub> | R <sub>12</sub> | R <sub>11</sub> | R <sub>10</sub> | R <sub>9</sub> | R <sub>8</sub> | R <sub>7</sub> | R <sub>6</sub> | R <sub>5</sub> | R <sub>4</sub> | R <sub>3</sub> | R <sub>2</sub> | R <sub>1</sub> | R <sub>O</sub> |

This example causes a direct branch to step 01C5 in the microprogram without meeting any logic conditions.

#### 4) Ram Address Instructions

Load auxiliary instructions unconditionally preset a RAM address specified by  $R_7 - R_0$  (AD<sub>7</sub> - AD<sub>0</sub>), using  $R_8$  (AD<sub>8</sub>) as a chip enable.

The LOAD AUXILIARY instructions are as follows:

LOAD AUXILIARY 8CXX

(DATA BUFFER): 1 0 0 0 1 1 0 0 X X X X X X X X

LOAD AUXILIARY 8DXX

(WORK BUFFER): 1 0 0 0 1 1 0 1 X X X X X X X X

Where X = new RAM address bits.

EXAMPLE: 8D20<sub>16</sub> (Load Auxiliary; Work Buffer)

| HEX 8           |                 |                 |                 |                 | HE              | K D            |                | HEX 2 HEX      |                |                |                |                | EX 0           | 0              |                |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| 1               | 0               | 0               | 0               | 1               | 1               | 0              | 1              | 0              | 0              | 1              | 0              | 0              | 0              | 0              | 0              |

| R <sub>15</sub> | R <sub>14</sub> | R <sub>13</sub> | R <sub>12</sub> | R <sub>11</sub> | R <sub>10</sub> | R <sub>9</sub> | R <sub>8</sub> | R <sub>7</sub> | R <sub>6</sub> | R <sub>5</sub> | R <sub>4</sub> | R <sub>3</sub> | R <sub>2</sub> | R <sub>1</sub> | R <sub>O</sub> |

This example presets RAM address to  $20_{16}$ ; bit  $R_8 = 1$  selects the Work Buffer RAM integrated circuits. Location 20 in the Work Buffer is the location for storage of the track header byte read from each disk sector.  $8CXX_{16}$  presets to any location within the R/W Data Buffer in RAM.

#### 5) Control Instructions

Control instructions are used to perform operations external to the microprocessor, such as sending a strobe to the 2200 CPU, or loading a R/W head in a Shugart disk drive.

The Control instructions are as follows:

EXAMPLE: FC10 (Control 2)

|                 | HE              | K F             |                 |                 | HE              | X C            |                | HEX 1 HEX      |                |                |                |                | EX 0           | 0              |                |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| 1               | 1               | 1               | 1               | 1               | 1               | 0              | 0              | 0              | 0              | 0              | 1              | 0              | 0              | 0              | 0              |

| R <sub>15</sub> | R <sub>14</sub> | R <sub>13</sub> | R <sub>12</sub> | R <sub>11</sub> | R <sub>10</sub> | R <sub>9</sub> | R <sub>8</sub> | R <sub>7</sub> | R <sub>6</sub> | R <sub>5</sub> | R <sub>4</sub> | R <sub>3</sub> | R <sub>2</sub> | R <sub>1</sub> | R <sub>O</sub> |

This instruction causes one strobe and one byte of data input to be sent to the CPU, as specified by the Control Operand  $10_{16}^{\, \circ}$

# 2.2.3.3 Typical Microprogram

The following microprogram is the prime routine for the WCS microprocessor. The prime routine consisting of 27 steps is initiated whenever the disk unit is turned on, the RESET key on the 2200 is depressed or the format button is depressed. Refer to text at end of program for a more detailed explanation of some of the actions that occur in the program.

# SAMPLE MICROPROGRAM: WCS PRIME ROUTINE

| STEP<br>(IN HEX) | HEX<br>CODE | INSTRUCTION    | COMMENT                                                                                                                                                   |

|------------------|-------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000             | FC04        | CNTRL 2/04     | Select Disk #1                                                                                                                                            |

| 0001             | F800        | A AND IMM      | Clear A Register (Immediate Operand = 0's).                                                                                                               |

| 0002             | 8D00        | Load Auxiliary | Select RAM address                                                                                                                                        |

| 0003             | 1400        | A to M(+1)     | Take zeroes in A register and transfer to current RAM location then increment (+1) to next RAM address. This clears locations 00-FF of the Work Register. |

| 0004 | A223 | BOTL           | (Branch to 0003 IF STO-2  (AD <sub>8</sub> ) is ON). This causes a loop which increments and clears each RAM location in the work buffer (256-511) per step 0003 comments.                                           |

|------|------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0005 | 1400 | A to M(+1)     | Same as step 0003 except clear data buffer (RAM locations 0-255). Note that when RAM address =111111111, adding (incrementing) RAM address brings the clear operation to RAM location 000000000 (MSB carry not used) |

| 0006 | B2D5 | BOFL           | (Branch to step 0005 IF ST0-2 (AD <sub>8</sub> ) is OFF). This causes a loop similar to steps 0003 and 0004. Per comments for step 0005 the RAM data buffer is cleared.                                              |

| 0007 | C803 | A OR IMM       | Immediate Operand = HEX 03;<br>therefore, HEX 03 is transferred<br>to the A register.                                                                                                                                |

| 0008 | 8DE8 | LOAD AUXILIARY | RAM address is preset to location E8 <sub>16</sub> (or 488 <sub>10</sub> ) which is the lst HEX 03 byte for disk sector format.                                                                                      |

| 0009 | 1000 | A to M(N)      | Transfer HEX 03 to current RAM location (Work Buffer, step 488 <sub>10</sub> ). No change (N) in RAM address.                                                                                                        |

| 000A  | 8DFF  | LOAD AUXILIARY | RAM address is preset to location FF <sub>16</sub> (or 511 <sub>10</sub> ) |

|-------|-------|----------------|----------------------------------------------------------------------------|

|       |       |                | which is the HEX 03 byte                                                   |

|       |       |                | for disk sector Write                                                      |

|       |       |                | operations; this is also                                                   |

|       |       |                | the second HEX 03 in sector                                                |

|       |       |                | format.                                                                    |

|       |       |                |                                                                            |

| 000В  | 1000  | A to M(N)      | HEX 03 (per comments for                                                   |

|       |       |                | step 000A) transferred to                                                  |

|       |       |                | RAM work buffer location 51110.                                            |

|       |       |                | 10                                                                         |

| 000C  | A74E  | BlTH           | Branch to step 000E IF bit 7                                               |

|       |       |                | (carry) is ON, indicating that                                             |

|       |       |                | Format Button has been depressed.                                          |

|       |       |                |                                                                            |

| 000D  | 88C8  | U.B.           | Assuming FORMAT has not been                                               |

|       |       |                | initiated, unconditionally                                                 |

|       |       |                | branch to step 00C8 to continue                                            |

|       |       |                | PRIME routine.                                                             |

|       |       |                |                                                                            |

| 00C8  | FB00  | ST1 AND IMM    | Immediate Operand -00                                                      |

| 0000  | T BOO | SII AND I'M    | Immediate Operand =00 <sub>16</sub> to clear carry.                        |

|       |       |                | to clear carry.                                                            |

| 00C9  | EC00  | CNTRL1         | Clear Busy indicator to CPU.                                               |

|       |       |                |                                                                            |

| 00CA  | FC00  | CNTRL2         | Clear Disk Select.                                                         |

|       |       |                |                                                                            |

| 00СВ  | 8C00  | LOAD AUXILIARY | R/W data buffer.                                                           |

|       |       |                |                                                                            |

| 00CC  | F800  | A AND IMM      | Clear A register.                                                          |

|       |       |                |                                                                            |

| 00CD  | 8D30  | LOAD AUXILIARY | Location of Error Count.                                                   |

|       |       |                |                                                                            |

| 00CE  | 1400  | A to M(+1)     | Clear Error Count.                                                         |

|       |       |                |                                                                            |

| 00 CF | 1400  | A to M(+1)     | Clear Status.                                                              |

| 00D0 | 1400 | A to M(+1)     | Clear Format Retry Count.                                             |

|------|------|----------------|-----------------------------------------------------------------------|

| 00D1 | 1400 | A to M(+1)     | Clear loc. 33 <sub>16</sub> in work buffer.                           |

| 00D2 | 1400 | A to M(+1)     | Clear spare loc. in work buffer.                                      |

| 00D3 | 8DOF | LOAD AUXILIARY | Location of 🐠 byte to be sent to CPU.                                 |

| 00D4 | A624 | вотн           | Branch to step 00D4 IF bit 6 of $ST_0$ is ON. (Look for 2200 strobe). |

The comments provide a basic explanation of what the instruction does, however the reasons are not always evident. This paragraph helps explain the reasons behind the steps executed in a prime routine.

| STEP | REASON                                                                                                                                                                                                                                                                                                                                          |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000 | Disk #1 is always selected. It is assumed that disk #1 will be used.                                                                                                                                                                                                                                                                            |

| 0001 | Clears the A register. A clearing process has now begun to set all pertinent registers to zero.                                                                                                                                                                                                                                                 |

| 0002 | Selects location 00 of the RAM's work buffer area. The next instruction will start a routine that will clear the 256 locations in the RAM.                                                                                                                                                                                                      |

| 0003 | Takes the zeroes from the A register and transfers them to location 00 of the RAM then increments RAM address.                                                                                                                                                                                                                                  |

| 0004 | Branch Ø = TL. Branch to step 0003 if STO-2 is on (AD8). The 23 of the code A223 indicates a mask of 2 and a branch to 3. The AD8 is always turned on by a Load Aux. command and this was done in step 0002. L99-3 turns on AD8 during a Load Aux. to the work buffer. This branch command causes a loop between steps 3 and 4 to clear the 256 |

locations per step 3 comment.

| 0005 | Same as step 0003 except clear data buffer (RAM locations 0-255). Note that when RAM address = 111111111, adding (incrementing) RAM address brings the clear operation to RAM location 000000000 (MSB carry not used).                                                                           |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0006 | (Branch to step 0005 IF bit 2 of $ST_0$ (AD <sub>8</sub> ) is OFF). This causes a loop similar to steps 0003 and 0004. Per comments for step 0005 the RAM data buffer is cleared.                                                                                                                |

| 0007 | The value HEX 03 is transferred to the empty A register by an OR Immediate. (The 03 is used when formatting a disk; this code is written in every sector as an aid in locating data on a write and read.)                                                                                        |

| 0008 | The RAM address is preset to location 8DE8 (488) which is the first HEX 03 byte for disk sector format.                                                                                                                                                                                          |

| 0009 | Transfers the 03 to the present RAM location without increment or decrement.                                                                                                                                                                                                                     |

| 000A | The RAM address is preset to location 8DFF (511) which is the 03 byte for disk write; this is also the second 03 in sector format.                                                                                                                                                               |

| 000В | Same as step 0009 but location 8DFF (511).                                                                                                                                                                                                                                                       |

| 000C | Branch to step 000E if bit 7 of ST1 register is on (the carry bit). The carry bit has several uses, one of which is being a flag to indicate that the format button was depressed. If the carry bit is on, the program branches to step 0190 to continue the format routine, otherwise continue. |

| 000Д | Assuming format has not been initiated, unconditionally branch to step 00C8 to continue prime routine.                                                                                                                                                                                           |

| When the microprogram was first written, steps C8 and C9     |

|--------------------------------------------------------------|

| contained the operations that steps D3 and D4 now contain;   |

| however, due to necessary modifications in the microprogram, |

| codes were added to steps C8 through D2 for use in another   |

| routine. Consequently, the unconditional branch to C8        |

| from OD was never changed to read "branch to D3." Therefore  |

| steps C8 through D2 are executed during a prime routine but  |

| are not necessary.                                           |

|                                                              |

OOD3 This Load Aux. presets the RAM address to location 8D0F preparing to receive a strobe from the 2200.

00D4 Branch to step 00D4 (branch on itself) until the 2200 strobe bit is sensed by STO-6.

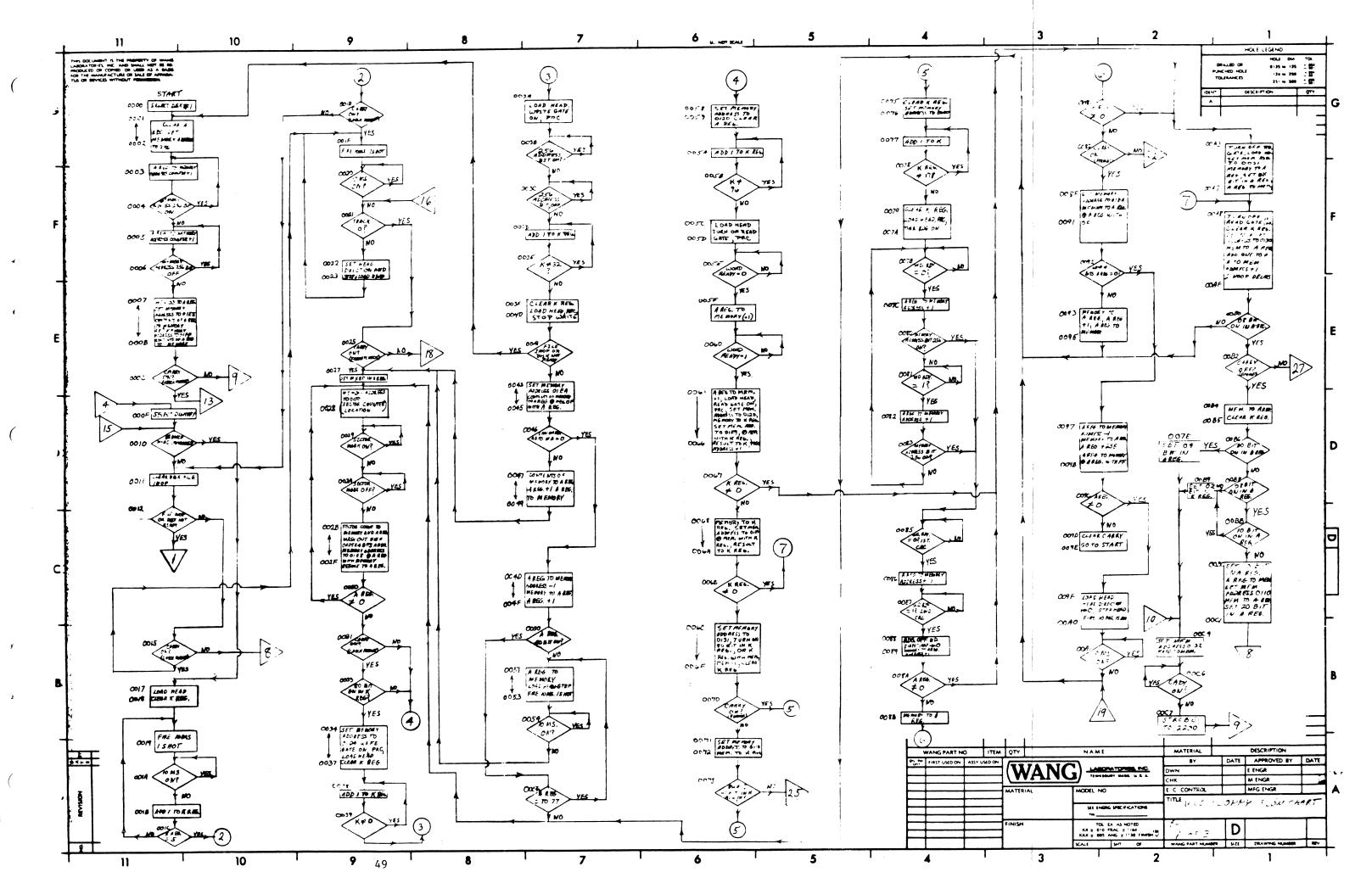

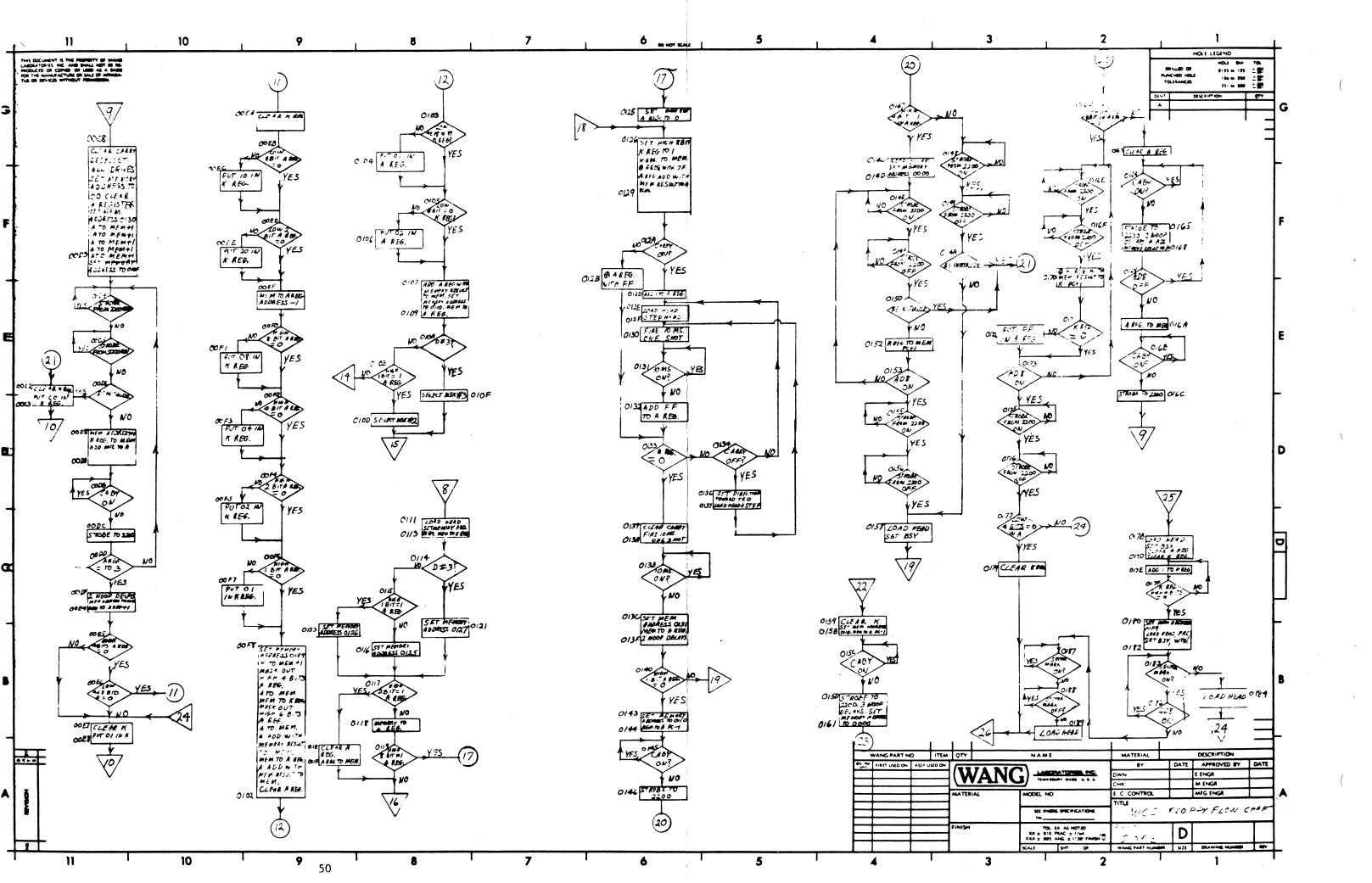

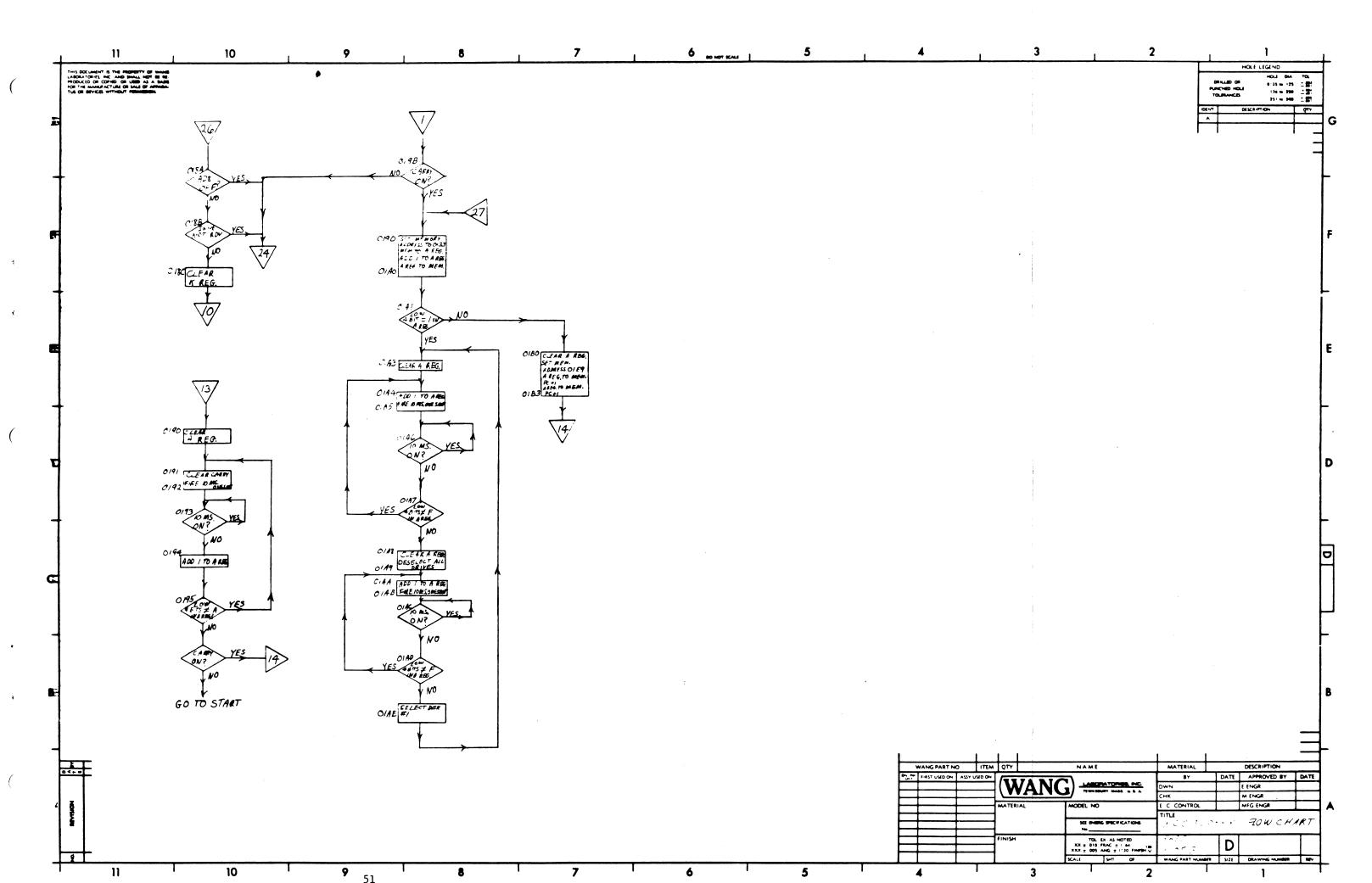

## 2.2.4 MODEL 2270 MICROPROGRAM

This section contains the complete Model 2270 microprogram with flow charts. To aid in following the Format, Write and Read routines, these routines are listed in abbreviated form below.

# FORMAT - WITH HEAD UNLOADED

- 1) Prime routine 0000-000C.

- 2) Format 000E.

- 3) 100 ms delay 0190-0198.

- 4) Select disk #1 000F-0010.

- 5) Load head with 50 ms delay 0017-001D.

- 6) Clear file inop. 0011-0012.

- 7) Br. to 0015 if no error 0012.

- 8) Br. to 001F if carry on 0015.

- 9) Move head to track 0 001F-0025.

- 10) Find requested sector 0027-0031.

- 11) Write format 0033-0041.

- 12) Checking and incrementing sectors 0043-004A.

- 13) When sector 15 is formatted, increment track #0046.

- 14) Checking and incrementing tracks 004D-0057.

- 15) When entire disk is formatted branch to 0058 from 0032.

- 16) Read header bytes and store in RAM 0058-0070.

- 17) Read routine for format 0075-0088.

- 18) Check CRC 0089-008D.

- 19) Check sector count for format read 008F-0096.

- 20) Check track count and step head 0097-00A2.

- 21) When finished reading format, branch to 0000 from 009E.

- 22) Prime routine 0000-000C.

- 23) No format 000D.

- 24) Prime continued 00C8-00D4.

## WRITE-WITH HEAD UNLOADED AND OVER TRACK ZERO

- 1) Prime 0000-000C.

- 2) No format 000D.

- 3) Prime continued 00C8-00D4.

- 4) Three initial address bytes from CPU 00D4-00DE.

- 5) Check for illegal address OODF-OOE6.

- 6) Track and sector conversion 00EA-0107.

- 7) Select desired disk from conversion 0108-0110.

- 8) Clear file inop. 0010.

- 9) Load head, 50 ms delay 0017-001E.

- 10) Clear file inop. 0011-0012.

- 11) Load head, 50 ms delay 0015-0016.

- 12) Load head and select appropriate track address 0111-011D.

- 13) Step head to desired track 0125-013B.

- 14) Head moved previously? Possible retry 013C-0140.

- 15) Answer last address byte 0143-0147.

- 16) Data from CPU (write) 014C-0154.

- 17) Accept LRC byte from CPU 0155-0158.

- 18) Find requested hardware sector 0028-0032.

- 19) Read header bytes and store in RAM 0058-0063.

- 20) Compare header bytes with requested address 0064-0074.

- 21) Write routine 017B-018D.

- 22) First and last (error) strobe to CPU 00C4-00C7.