# Table of Contents

| Reader's Guide                                 | 3 |

|------------------------------------------------|---|

| I. General Background Concepts                 |   |

| A. The Task of an Interface                    | 1 |

| B. Software                                    |   |

| 1. Data Representations in the Computer        | 5 |

| 2. Input/Output Data Representations           | 7 |

| 3. The Four Types of HP Interfaces             | 7 |

| 4. The Data Transfer Process                   | 9 |

| C. Hardware                                    | ) |

| 1. Logic Levels and TTL Implementations        | ) |

| 2. Gates, Latches, and Flipflops               | 2 |

| 3. The Use of Jumpers                          | 5 |

| II. Programming for Interfacing Operations     | 7 |

| A. Standard I/O Programming                    | 7 |

| 1. Register Operational Model of an Interface  | 7 |

| 2. Select Codes                                | 8 |

| 3. Direct Register Access                      | 8 |

| 4. Binary I/O Operations                       | 9 |

| 5. Formatted 1/0 Operations 19                 | 9 |

| 6. The Status and Control Registers            | 1 |

| B. Interrupt I/O Programming                   | 1 |

| 1. The Uses of Interrupt                       | 1 |

| 2. Data Transfers with Slow Devices            | 2 |

| 3. Further Data Transfer Examples              | 4 |

| 4. Data Transfers with Fast Devices            | б |

| 5. User Programmed Service Routines            | 7 |

| 6. Interrupt Priorities                        | 9 |

| C. Special Programming Topics                  | 1 |

| 1. Formatting the Internal Printer and Display | 1 |

| 2. Interface ID and Card Types                 | 2 |

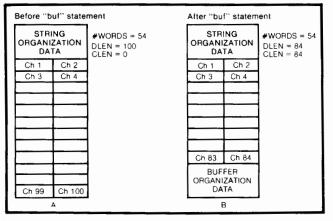

| 3. Using Strings as Buffers                    | 2 |

| 4. Buffer Use Outside of the I/O Process       | 3 |

| 5. Use of the Control Register                 | 4 |

| III. HP Interface Cards                        | 7 |

| A. Interfacing and the Computer I/O Bus        | 7 |

| B. The 98032A Bit Parallel Interface           | 9 |

| 1. General Operational Characteristics         |   |

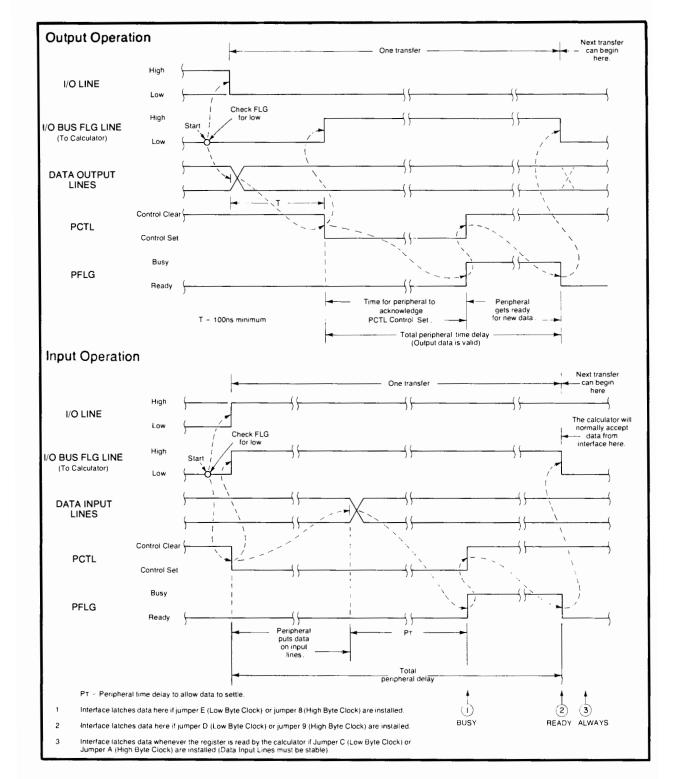

| 2. The Handshake Process                       | 2 |

| 3. Word and Byte Modes of Operation            | 4 |

| 4. Data Inversion and the Transfer Process     | 6 |

| C. The 98033A BCD Interface                |

|--------------------------------------------|

| 1. BCD Instruments                         |

| 2. 98033A BCD Formats                      |

| 3. The 98033A Interface Registers          |

| 4. The 98033A Handshake Process            |

| 5. Connecting BCD Devices to the 98033A 49 |

| D. The 98034A HP-IB Interface              |

| 1. An Introduction to the HP-IB            |

| 2. The Structure of the HP-IB              |

| 3. Addressing Bus Devices                  |

| 4. Data Operations on the HP-IB            |

| 5. Extended HP-IB Control Features         |

| 6. Using the 98034A Interface              |

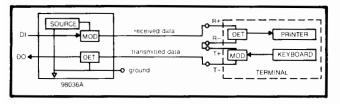

| E. The 98036A Serial I/O Interface         |

| 1. An Introduction to Serial I/O           |

| 2. Data Transmission Using Serial I/O 62   |

| 3. Control Lines and the RS-232-C Standard |

| 4. The 98036A Serial I/O Interface         |

| 5. Programming with the 98036A Interface   |

| 6. RS-232-C vs. Current Loop Operation     |

| Appendix                                   |

| A. ASCII Character Set                     |

| B. 98032A Register Map                     |

| 98032A Jumper Options                      |

| C. 98033A Register Map                     |

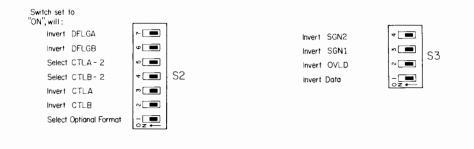

| 98033A Switch Configurations               |

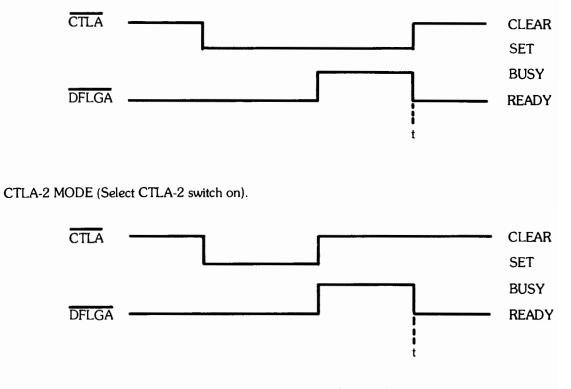

| 98033A Handshake Diagram                   |

| D. 98034A Register Map                     |

| E. 98034A Operational Sequences            |

| F. 98036A Register Map                     |

| G. Keyboard / Display / Printer Registers  |

| H. Interfacing Bibliography                |

| Index                                      |

# HP Computer Museum www.hpmuseum.net

For research and education purposes only.

# **Reader's Guide**

This guide for interfacing peripheral devices to Hewlett-Packard desktop computers is designed to provide additional information which may be helpful to the user who needs to interface his peripheral equipment to HP desktop computers and/or program the resultant system for interfacing applications.

It is not intended to be a replacement for either the operating and programming manuals for the desktop computer, or the installation and service manuals for the individual interface cards. The maximum benefit can be obtained from this guide if these individual manuals are studied first. They provide the user with a detailed description of the individual operations available from the computer, and of the various functions provided by each interface card. At the same time they assume that the user has a certain level of knowledge about the programming techniques (software) and electronics (hardware) involved in interfacing applications.

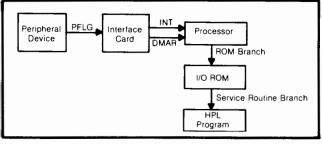

The purpose of this interfacing guide is twofold. First, it is intended to provide some introductory hardware and software concepts which are assumed by the manuals, but with which the user may not have previous experience. The second purpose of the guide is to present an alternative approach to explaining the operations discussed in these manuals. For example, while the computer operating manual discusses the use and the detailed syntax of those programming statements associated with interrupt operations, the guide expands this information by discussing how interrupts are implemented, and when they should and should not be used. The guide also presents introductory information on such topics as the Hewlett-Packard Interface Bus (HP-IB) and serial I/O which is not available in the manuals for these interface cards. In addition, since this guide is not intended to describe a single computer, interface card, or peripheral device as a stand-alone piece of equipment, it can discuss the use of all three elements as an integrated system.

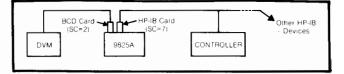

The guide is primarily oriented around the HP 9825A Desktop Computer and four of its associated interface cards: the 98032A, 98033A, 98034A, and 98036A. Example programs are presented in HPL, the high-level programming language of the 9825A. However, a majority of the concepts that are discussed apply to interfacing in general and the user should find a reading of this guide helpful in understanding the operations of other HP desktop computers and interface cards. For example, the HP System 45 Desktop Computer uses the same set of interface cards, and operates in a manner similar to the 9825A with the HPL statements replaced by their BASIC language equivalents.

Section I of this guide presents general background information useful for interfacing applications. For the engineer not experienced in software concepts, information is given on computer data representations and I/O (input/output) programming. For the programmer not experienced in hardware concepts, topics such as logic levels, TTL gates, latches, and flip-flops are discussed. The reader with a background in hardware and software can proceed directly to Section II.

In Section II, the discussion is centered around programming for interfacing applications. It is not the purpose of this section to teach the HPL programming language or to present the detailed syntax and restrictions of those programming statements related to 1/O operations. This is the purpose of the operating manuals. Instead, the guide tries to give the user an appreciation for what takes place on the low level when the high level programming statements are executed. It is the philosophy of this guide that if the user understands these low level operations, many of the observations that appear to be strange from the high level will lose much of their mystery. Also, such an understanding should allow the reader to make more intelligent use of the power available in desktop computer systems.

Section III concentrates on the individual interface cards themselves. Here again, an alternative approach to the installation and service manuals for these cards is taken, and a register-operational model of these interfaces is developed. All of the functions provided by these cards are described in terms of sequences of register operations.

The Appendices contain a collection of useful tables, diagrams, and timing information, along with a selected bibliography of references for additional reading.

# Section I General Background Concepts

# A. The Task of an Interface (an Overview)

In discussing interfacing peripheral devices to a desktop computer, the first question that naturally arises is "What does an interface do, and why is it necessary?" In order to answer this question, it is helpful to understand some of the characteristics of the computer and of the peripheral devices which it is to control.

A computer by itself is not a very useful device. Its power comes from its ability to accept inputs from an outside source, modify these inputs according to a given set of rules (as expressed by the program in the computer), and output the results of these computations to some external device. Some typical input devices are punched card readers, tape readers, digitizers, and digital voltmeters. Output devices would include printers, tape punches, plotters, and graphic displays. In addition, there is a seemingly endless list of special-purpose sensing devices (input) and control equipment (output) designed to perform particular tasks.

Ideally, every such device that was built would conform to some standard that specified all the characteristics of its I/O (Input/Output) connection, thus making all such devices "plug-to-plug" compatible. Unfortunately, no such standard exists. As a result, four major areas of incompatibility arise when one attempts to connect a peripheral device to a computing controller. It is the task of the interface to provide the necessary compatability in these areas.

#### Mechanical Compatibility:

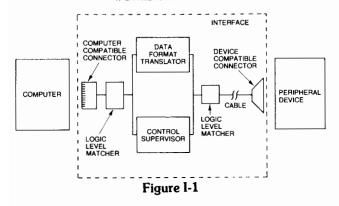

The simplest requirement for the interface to meet is that of providing mechanical compatability. This consists of merely supplying the appropriate connector at each end of the interface, and wiring the connectors in INTERFACE FUNCTIONAL DIAGRAM

such a way that each input line at one end of the interface is connected to its corresponding output line at the other end (see Figure I-1). If there were no other incompatabilities to overcome, this pair of cross-wired connectors would constitute the entire interface. In practice, things are rarely this simple.

#### **Electrical Compatibility:**

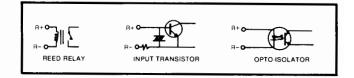

A second function of an interface is to match the electrical characteristics (i.e., current and voltage levels, sometimes called logic levels) of the computer to those of its peripheral. Since HP desktop computers and their associated interfaces are designed using compatible electronic logic levels (called TTL), the logic-levelmatcher functional block at the computer end of the generalized interface shown in Figure I-1 is not necessary. Fortunately, many peripheral devices also use TTL levels in their circuitry. A discussion of TTL levels is contained in section IC1, along with information on interfacing devices that use other voltage levels.

#### Data Compatibility:

Once an interface has made the computer and its peripheral device mechanically and electrically compatible, they are capable of exchanging messages as electrical signals over wires called data lines. But just as two humans who do not speak the same language need a translator, data messages between a computer and its peripheral may also require some sort of format translation. The computer with its versatile programming capability, will usually perform this function. But in some cases, this task is given to the interface for reasons of speed. The BCD and the Bit Serial interfaces are examples of cases where the task of data reformatting is assigned to the interface. More discussions of this data translation process are contained in the sections describing these interfaces.

#### Timing Compatibility:

Humans have the remarkable ability to talk and listen at the same time (or at least in rapid succession) without losing too much of the content of the conversation. Our speaking and listening rates are also well matched. Computers and their peripheral devices, on the other hand, have such a wide range of operating speeds that a much more orderly mechanism is required for successful transfer of data messages. Providing timing compatability (sometimes called the handshake function), along with other miscellaneous control operations, is the fourth major task of the interface.

This overview of the various functions of an interface has been very general. The sections that follow give more detailed information on the way in which HP interfaces implement each of these functions, along with other background information on HP desktop computer architecture, data formats, and other topics related to interfacing.

# **B.** Software

# 1. Data Representations in the Computer

Since the primary purpose of interfacing is to exchange data between a computing controller and its peripheral devices, or between two computers, it would be helpful to first look at how this data is represented within the computer.

The memory of any digital computing device is made up of a large number of storage locations called bits. The number of bits that make up the memory can vary from a few hundred in a small hand-held calculator to several million in large computers. Each of these bits (bit is an abbreviation for binary digit) can be set to and will maintain one of two states. Depending on the meaning assigned to it, the bit may represent yes or no, on or off, one or zero, true or false, etc. A single bit by itself, however, is only capable of representing simple two-state information.

To store more complex information, it is necessary to group several bits together into a logical package. For example, if we wish to represent the decimal digits 0 through 9 in the computer memory, we could collect bits into groups of four, and use the following encoding scheme.

|  | 0<br>00 | )<br>00 | $\begin{array}{c}1\\0001\end{array}$ | 2<br>0010 | 3<br>0011 | 4<br>0100 | 5<br>0101 | 6<br>0110 | 7<br>0111 | 8<br>1000 | 9<br>1001 |

|--|---------|---------|--------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

|--|---------|---------|--------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Figure I | •2 |

|----------|----|

|----------|----|

Since each bit can take on two states (represented here by the symbols 0 and 1), a group of N bits can take on  $2^{N}$  states. In this example, the groups of four bits are capable of representing  $2^{4} = 16$  states. Since there are only 10 decimal digits to be represented, we do not use 6 of the possible 16 states. To represent alphabetical information, we would need to have a representation for each of the 26 letters of the English alphabet. This would require groups of 5 bits each, since  $2^{5} = 32$ . To represent both decimal digits and English letters (36 characters total) would require 6 bits.

In the example above, we could just as easily have assigned the following encoding scheme: 0=0110, 1=1011, 2=0000, 3=0011, 4=0101, etc. And indeed, many computers use an internal representation of letters, numbers, and symbols which will make the task of performing the desired operations on these items as simple as possible. This will vary from computer to computer depending on how it will manipulate this data. This variety of internal representations causes no problem until two computers or a computer and its peripheral need to exchange data. Then it becomes necessary that both devices use the same data representation, or that one of the devices is capable of translating between the two representations.

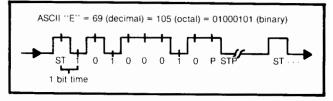

A third alternative is that each device may use whatever internal representation is most convenient, but that all data will be input or output in some standard representation. There are several of these socalled standard representations that are becoming popular and widely accepted, depending on the particular job. For example, if only numeric data is to be represented, the encoding scheme first given in our example is widely used. This scheme is called BCD or Binary Coded Decimal representation. One of the most general and widely-used encoding schemes for data exchange is known as ASCII (pronounced as'ki), which is an acronym for American Standard Code for Information Interchange. The ASCII code commonly uses 8-bit packages and has representations for numerical digits, upper-case, and lower-case letters, common typewriter symbols (#, %, %, &,  $< \ddagger =$ , ?, etc.), and special control characters (carriage return, line feed, etc.). A complete table of the ASCII encoding scheme is found in the Appendix. A large number of peripheral devices made by HP and other manufacturers use ASCII code for sending and receiving alpha-numeric data.

HP desktop computers also use 8-bit ASCII code for the internal representation of alpha-numeric data (called strings). These 8-bit packages are so convenient for data representations that they have been given the name byte. Indeed, it is now quite common to measure memory sizes in terms of these 8-bit bytes.

Although 8-bit bytes are ideal for storage and transfer of alpha-numeric strings of characters, they are not very well suited for internal representation of numeric values. It is difficult to perform arithmetic operations on numbers that are expressed as strings of ASCII symbols.

The simplest method for storing and manipulating numeric values uses the so-called binary representation. In this method, a group of N bits is used to represent a number, and each position in the group has a value which is a power of two. For example, to represent the number 98 as an 8-bit binary number, we note that when broken into powers of two, 98 = 64 + 32 + 2 as shown in Figure 1-3.

| bit #      | 7   |    | 5  |    |   |   |   |   |  |

|------------|-----|----|----|----|---|---|---|---|--|

| value      | 128 | 64 | 32 | 16 | 8 | 4 | 2 | 1 |  |

| Eg., 98 =  | 0   | 1  | 1  | 0  | 0 | 0 | 1 | 0 |  |

| Figure 1-3 |     |    |    |    |   |   |   |   |  |

Since any number can be expressed as a sum of powers of two in only one way, this binary representation yields a unique pattern for each number. In numbering the bits, we have called the least significant bit "bit zero". It is also common to find the bits numbered starting from one. Most of the manuals and documentation for HP desktop computers number the bits starting with zero, since this makes the value of the n-th bit position equal to  $2^n$ . But being aware that two conventions for numbering the bits are in common usage could help to avoid possible confusion.

In the example given above, the largest number that can be represented by the 8-bits is 255. Thus, we say that the range of an 8-bit binary representation is zero to 255 (often written as [0,255]). If we need to represent wider ranges of values, we can use larger groupings of bits. Indeed, all HP desktop computers (except the 9815) use groups of 16 bits (called words) to represent binary data inside the machine. These binary values are used for such things as counters, limit values (as in saving the size of an array), and pointers to locations within the memory.

One limitation of the binary system described, however, is that only positive integers are represented. Negative values can be easily incorporated into the system if we pick one bit (usually the highest one) to represent the sign of the number. For example, if we use an 8-bit byte and let bit 7 be the sign bit, using the convention that 0 is plus and 1 is minus, then 00000101 would represent a +5 while 10000101 would represent -5. This convention is called the "sign/magnitude" binary representation. It is simple to understand, but unfortunately it causes difficulties in computation. This is because the hardware processor that does arithmetic on these numbers must have a subtractor as well as an adder. This makes the processor more costly and less efficient, since it must first decide (from the sign bits) whether an add or subtract must be done.

An alternative representation for both positive and negative binary values is called the "two's complement form". In this form, positive values have the same form as in the sign/magnitude representation. Negative numbers, however, are formed by the following rule: complement the number (i.e., replace all ones with zeros and zeros with ones) and add one (ignoring any carry out of the highest bit). For example, +5 is still represented by 00000101. Minus 5 is gotton by complementing (11111010) and adding one (11111011). Thus, in an 8-bit, 2's-complement representation -5 = 11111011. Notice that if we apply the complement-and-add-one rule to the representation for -, we get back the representation for +5, so that the rule is symmetric. The advantage of 2's-complement notation is that only an adder is required. For example, to calculate the value of 7-5, we rewrite it as 7 + (-5) = 00000111 + 11111011 =00000010 = 2. Thus we subtracted 5 from 7 using only a binary adder.

The table below gives an example of all values that can be represented by a 3-bit binary number in 2's-complement form.

| -4         | -3  | -2  | -1  | 0   | 1   | 2   | 3   |

|------------|-----|-----|-----|-----|-----|-----|-----|

| 100        | 101 | 110 | 111 | 000 | 001 | 010 | 011 |

| Figure I-4 |     |     |     |     |     |     |     |

In general, an N-bit, 2's-complement form can represent all integers in the range  $[-2^{N-1}, +2^{N-1}-1]$ . For the 16-bit binary values that are used internally for counters and pointers, this range is [-32768, 32767]. If larger ranges of integers need to be represented, packages of larger number of bits could be used. Notice that the representations of values is not independent of the number of bits used in the representation. For example, in the table above, 101 represents a -3 when using a 3-bit, 2's-complement format; but 101 represents a +5 in a system using 4 or more bits.

#### **EXAMPLES**

Show that in 16-bit, 2's-complement form, the two decimal values +5000 and -5000 are represented by 0001001110001000 and 1110110001111000 respectively.

0001001110001000 = 8 + 128 + 256 + 512 + 4096 = 5000.

To find the decimal equivalent of 1110110001111000, first convert to its positive equivalent by complementing the bits (yielding 0001001110000111) and add one to get 0001001110001000. Since this is the binary form of +5000 as found above, the original pattern represents -5000.

2. Show that the binary numbers below have the equivalent decimal representations given.

| 0101011011001110 = 22222 | 1010100100110010 = -2222  |

|--------------------------|---------------------------|

| 0011000000111001 = 12345 | 1100111111000111 = -12345 |

| 111111111111111111 = -1  | 11111111111110110 = -10   |

| 100000000000001 = -32767 | 100000000000000 = -32768  |

Notice that when the "complement and add one" operation is performed on the binary equivalent of -32768, the same binary pattern is re-generated. This is because there is no 16-bit, 2's-complement representation for a +32768. Thus, when using the rule of converting between positive and negative binary values, a one in the sign bit and all other bits being zeros must be treated as a special case.

We still have not solved the problem of representing non-integer values. In the decimal system we handle this by the use of a decimal point. For example,

12.75 = 1x(10) + 2x(1) + 7x(1/10) + 5x(1/100).

We could represent this same number in binary by the use of a "binary point" as

$$12.75 = 1100.11 = 1x(8) + 1x(4) + Ox(2) + Ox(1) + 1x(1/2) + 1x(1/4) .$$

In each system, there are some numbers that cannot be exactly represented in a finite number of places. For example, the decimal representation of  $1/3 = 0.33333\cdots$  requires an infinite number of threes to represent exactly. Similarly, the binary representation of  $1/10 = 0.0001100110011\cdots$  cannot be represented exactly. Since most data presented to a computer from the real world is in decimal form (e.g., \$235.17), conversion to binary form for internal storage and computation often results in inaccuracy due to the lack of an exact representation. This inaccuracy is in addition to any roundoff errors introduced by the subsequent calculations performed on that value.

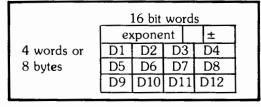

To get around this deficiency, numbers are stored within HP desktop computers in a decimal format. The structure of this format is shown below.

Each value occupies four 16-bit words (8 bytes). Each digit uses four bits and is in BCD format, with four digits packed into one 16-bit word. The sign and exponent of the number are encoded into the first word of the representation. Bit 0 is the sign of the value (0=plus, 1=minus), while bits 15-6 represent the exponent using a 10-bit, 2's-complement form. (Bits 5-1 are not used.) All calculations are done on this so-called "floating point" format, and the task of converting between this representation and a string of ASCII characters for I/O purposes is relatively straight forward.

#### **EXAMPLES**

- Calculate the four 16-bit words that are the internal representation of the following decimal values.

- (a) 2.71828182846?

| Answer: | 00000000000000000 | exponent=0, sign=+ |

|---------|-------------------|--------------------|

|         | 0010011100011000  | 2718               |

|         | 0010100000011000  | 2818               |

|         | 0010100001000110  | 2846               |

(b) -1234.56789?

| Answer: | 000000011000001  | exponent=3, sign=- |

|---------|------------------|--------------------|

|         | 0001001000110100 | 1 2 3 4            |

|         | 0101011001111000 | 5678               |

|         | 1001000000000000 | 9000               |

(c) -0.00123456789?

| Answer: | 1111111101000001 | exponent=-3, sign=- |

|---------|------------------|---------------------|

|         | 0001001000110100 | 1 2 3 4             |

|         | 0101011001111000 | 5678                |

|         | 1001000000000000 | 9000                |

# 2. Input/Output Data Representations

We just looked at data representations within HP desktop computers. The table below summarizes these representations.

| Data Type | Bits Used        | Representation                                       |  |  |

|-----------|------------------|------------------------------------------------------|--|--|

| Strings   | 8-bit bytes      | ASCII                                                |  |  |

| Numeric   | 16-bit words     | 2's-complement binary<br>(internal use only)         |  |  |

| Numeric   | 64-bit registers | rs Decimal floating-point<br>(user program variables |  |  |

#### Figure I-6

For I/O purposes, these internal representations must be converted into a format that can be understood by and is dependent upon the particular peripheral with which the computer is to communicate. Each peripheral can be categorized, for purposes of data transfer, by two characteristics: the number of bits required for each item of data transferred, and the format of those data bits (ASCII, binary, BCD, etc.). A small number of data types are sufficient to handle most peripheral devices, and HP desktop computers provide interfaces for each of these major categories. A detailed description of each of these interfaces is contained in later sections of this guide; and here we will merely look at the types of data formats that each interface card supports.

### 3. The Four Types of HP Interfaces

#### 98032A Bit Parallel Interface

Because of its great versatility, this card is the general -purpose interface used with most standard HP peripherals and many special-purpose devices supplied by the user. It can accommodate data items of up to 16-bits in parallel. Assume, as an example, that this interface card is being used to connect the computer to a printer which uses the ASCII character set. Each character to be sent to the printer would be encoded using the 8-bit ASCII representation shown in Appendix A. To send an entire message such as "The value of pi is 3.14159." to the printer, the characters would be sent one at a time in serial fashion to the printer. But the eight bits that represent each character would all be sent at once in parallel. That is, all eight bits would be presented to the printer at once, one on each of eight separate data lines. When all eight data lines are set to the proper pattern of ones and zeros to represent the character being sent, the printer is told that the data on the lines is now valid, the printer senses the pattern on those lines, and prints the ASCII character assigned to that particular pattern. When the printer indicates that it has completed the character just given to it, the computer then changes the data lines to represent the next character in the message and the cycle repeats. This method of data transfer is sometimes called "bit-parallel, character-serial transmission".

Notice that when using the ASCII code, only 8 of the 16 data lines are used. Other peripheral devices which use codes other than ASCII might use only a few or all 16 of the data lines to represent their data. It is also important to note that HP desktop computers only provide ASCII representations of 1/O data automatically. That is, when high-level 1/O statements (such as read and write) are used in a program, they generate and expect to receive data coded in the ASCII representation. If any other encoding scheme is used, it is up to the user's program to know the representation being used and to convert the bit patterns received into a form that can be used within the computer.

Sometimes this is a simple task. For example, if a peripheral device supplied data in the form of 16-bit, 2's-complement numbers, the program would read a 16-bit value, convert it to internal floating point representation (see Section IB1), and return the decimal equivalent of that value which would be a number in the range -32768 to +32767. Another device, however, might send only positive values using 16-bit binary representation. That is, it does not use the 2's-complement form, but rather all bits represent positive powers of two giving the 16-bit number a range of 0 to 65535. Since the rdb function only reads numbers in 16-bit, 2's-complement form, the following program segment would be required to do the necessary conversion.

37: rdb (4)  $\rightarrow$  A 38: if A< $\emptyset$ ; 65536 + A  $\rightarrow$  A

#### 98033A BCD Interface

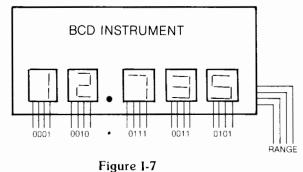

Data representations from input devices fall into three major categories. These are ASCII (directly supported by the read statement), binary values (obtained with the read binary function), and all other codes, which must be interpreted by the user's program. Of these other codes, one is in such common use that a special interface card has been developed to take the burden of data translation from the user's program. This code is called the BCD (Binary Coded Decimal) representation. It is typically used in measurement instruments such as a digital voltmeter (DVM). For example, assume that we have a DVM that is measuring a voltage level of 12.735 millivolts. The output connector of the DVM would supply four data lines for each digit in the reading (see Figure 1-7). Each of these digits would be encoded using the 4-bit BCD representation shown in Figure 1-2. In addition, a few data bits (typically 3 or 4) would be used to represent the range that the DVM is set to (i.e., volts, kilovolts, milivolts, etc.).

In using the 98032A Bit Parallel Interface to take a reading from this instrument, we would encounter two major problems. Since a 5 digit reading is represented by more than 16 bits, the DVM would need to deliver a reading in the form of two 16-bit packets. Our program would have to break up these two 16-bit patterns four bits at a time and convert them to digits and a range multiplier for the value being read, and then combine these digits and the multiplier to form a number that represented the reading that was taken. This would be a complex and time consuming task for the program.

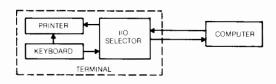

Instead, this task is performed by the 98033A BCD Interface. This card accepts in parallel from the device up to eight 4-bit BCD digits and a 4-bit multiplier, and then converts this reading into a sequence of ASCII characters (in our example, "12.735E-3") that can be directly read by the computer's ASCII read statement.

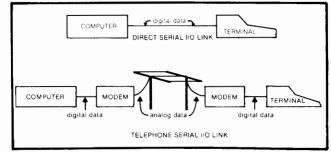

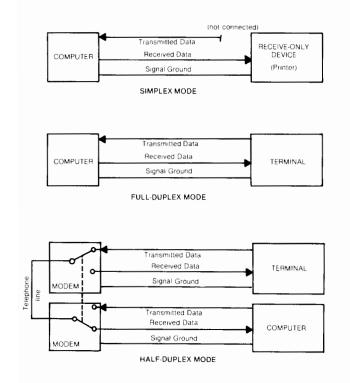

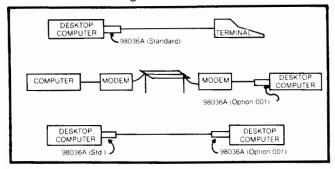

#### 98036A Serial I/O Interface

A new data representation problem arises in the area of data communications. Strictly speaking, any exchange of data between a computer and its peripheral devices could be called data communications; but this term is usually reserved to mean the exchange of data between two computers (or between a computer and a terminal) that are located at some distance from one another. If both machines are in the same building, they are usually connected by long cables. If they are in different buildings (or different cities) telephone lines might be used to make the connection. In either case, the cost of the connection rises rapidly with the number of bits that are sent in parallel. Therefore, a scheme has been devised that allows the exchanged information to be sent over a single data line.

Using this method, not only are the characters of the message sent in a serial fashion, but the bit patterns for each character are also sent serially, one bit after another along the single data line. This requires some rather sophisticated timing considerations which are handled by the interface card. This allows the program to treat the interface as a simple 8-bit parallel device. That is, the user writes his message to the interface as a sequence of 8-bit (usually ASCII) bytes, just as he would to the 98032A card. The Serial I/O interface then performs the task of converting each character to a bit-serial stream and sending it over the data communications line. For input, the interface receives a seguence of bits for each character, assembles them into a parallel 8-bit byte, and delivers this byte to the computer all at once.

More information about the particular capabilites of the 98036A card is contained in Section IIIE1.

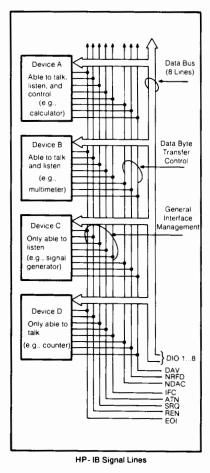

#### 98034A HP-IB Interface

The task of interfacing a peripheral device to the computer would be greatly simplified if the four areas of interfacing incompatability discussed in Section IA could be overcome. That is, if a standard were developed that completely specified the mechanical, electrical, data, and timing characteristics of an I/O bus, then all computers and peripheral devices that followed this standard would be "plug-to-plug" compatible.

Such a standard has been adopted by the Institute of Electrical and Electronic Engineers (IEEE 488-1975). This standard has become so popular that dozens of manufacturers are providing hundreds of devices which conform to its specifications and can be interfaced to one another by simply plugging them together. There is no special representation which must be used for data messages on this bus, although the vast majority of IEEE-488 devices have implemented ASCII as their encoding scheme.

The 98034A HP-IB (Hewlett-Packard Interface Bus) card interfaces HP desktop computers to the IEEE-488 bus. A more detailed description of the HP-IB is given in Section IIID1.

## 4. The Data Transfer Process

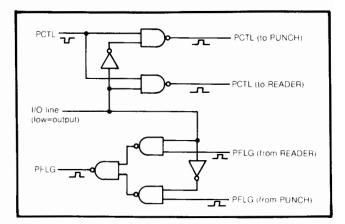

Up to now, we have been concerned with how the various bit patterns on the data lines are to be interpreted. We have talked about sending and receiving sequences of characters, but have not mentioned how this process is accomplished. The main difficulty involved is one of timing. If the speed of the computer and its peripheral are not exactly matched, the faster device will somehow have to slow down the pace of its I/O operations so that it will not get ahead of the slower device. This is accomplished through a mechanism known as "handshake". The detailed description of the handshake process is discussed in the sections on the interface cards, and here only the concept of the handshake will be considered.

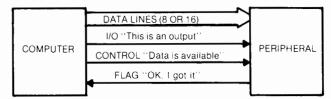

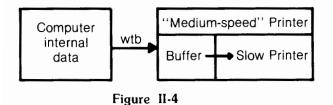

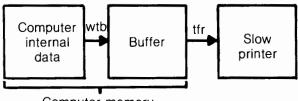

Handshake for the output process (Figure I-8) proceeds as follows. The first of a sequence of characters to be transmitted is placed on the data lines. When this operation is complete, the interface indicates that the data is valid by setting a special control line. When the peripheral detects that this control line is set, it raises another line called flag to indicate to the computer that it is momentarily going to go busy in order to process that character. It then takes the information from the data lines and processes it. This processing may involve printing a character, plotting a point, or whatever other function the peripheral device is designed to perform. Some devices do not operate from single characters, but wait until an entire sequence of characters is received to perform their actions. For example, the 9866A/B Thermal Line Printer contains a block of read/write memory called a buffer, into which characters to be printed are placed. For this device, the processing of most characters consists of merely placing that character in the buffer. Then when it receives a linefeed character (ASCII 10), it prints an entire line contained in its buffer at one time. In any case, when the processing of that character is complete, the peripheral lowers the flag line to indicate that it is again ready. The computer then places the next character on the data lines and the entire handshake process repeats again.

Figure I-8. Data Output Handshake

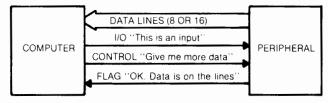

The sequence of events for input (Figure 1-9) is similar to that for output. On a separate I/O indicator line, the computer specifies that an input operation is to be performed, and then sets the control line. This time when the peripheral sees control go set, since the I/O line is indicating input<sup>\*</sup>, it knows that it is to supply the data. The peripheral first raises the flag line to indicate that it is busy, and goes to gather the requested data. This may involve taking a sample for a DVM, advancing a paper tape, digitizing an X,Y coordinate, or doing whatever the device was designed to do in order to

<sup>\*</sup> Throughout this guide, the terms input and output are always used with the computer as the point of reference. Thus, input means from the peripheral to the computer.

gather data. This data is then placed on the data lines by the peripheral and the flag line lowered to indicate that the data is now ready. The computer will then read the data and the handshake on one input character is complete. If a complete reading consists of several characters, the computer will again set the control line when it is ready for the next character and the process repeats.

Figure I-9. Data Input Handshake

It is important to note that in both the input and the output processes, the computer initiates the handshake procedure by setting the appropriate state of the I/O line and then setting control. Under no circumstances does the peripheral ever initiate a data transfer operation. This concept will be especially important when we discuss the interrupt process. Interrupts are always generated by the peripheral in response to a request from the computer, and not at the discretion of the peripheral device.

Finally, it should be mentioned that the concept of a handshake is a very general one and not limited to the description given here. Other schemes are possible and commonly used. This particular version of a three-wire handshake (I/O, control, flag) is adopted by the HP 98032A interface card and the one that should be understood when connecting this interface to peripheral devices.

Most data and control lines on the HP interface cards use negative-true logic. It is easy to tell whether negative-true or positive-true logic is being used for a particular line from the schematic diagram of the interface card, which is found at the back of the installation and service manual for that interface. If the name of the line (e.g., PFLG) appears with a bar drawn over the top of it, that line is using negative-true logic; otherwise it is using positive-true logic. For example, the 98032A interface has two general-purpose control lines called CTLØ and CTL1. The state of CTLØ is set from the program by use of the write control statement (wtc) whose syntax is:

wtc <select code>, <control byte>.

The least significant bit of the control byte is used to set  $CTL\emptyset$ . Since on the schematic diagram for this card, that line is labeled with a bar over it, it is using negative-true logic. Thus, the statement wtc 6,0 will set the  $CTL\emptyset$  line high, and wtc 6,1 will set it low.

# C. Hardware 1. Logic Levels and TTL Implementations

In previous sections we have used such phrases as putting data on the lines, setting the control line, and making the flag line go busy, without really saying how these things are electrically implemented by the interface. But when it comes time to wire the interface to a non-standard peripheral device, it is helpful to understand how the electronic circuitry of the interface card relates to the operational concepts we have been discussing. In this section we will discuss some of the electronic concepts necessary to understand that circuitry.

The two main electrical concepts involved are those of voltage and current. For our purposes here, it may be helpful to explain these concepts in terms of an analogy with a forced air heating system found in many houses. In this system, after the air has been heated, a blower is used to create a pressure that is higher than the surrounding atmospheric pressure in the rest of the house. This blower is connected through a series of air ducts to the outlet registers placed throughout the various rooms. Because the pressure at the blower is higher, the heated air is forced to flow through the ductwork and out the registers. The pressure at any point in the system is always at a level somewhere between the maximum pressure produced by the blower and the atmospheric pressure at the outlets, and is determined by how much resistance the air has encountered from the ductwork along its path from the blower to the point which we are measuring. More air will travel along those paths in the heating system that present a lower resistance to the air flow. Indeed, the homeowner can vary the resistance in various branches by opening and closing louvers at the registers, resulting in redistributing the airflow throughout the house.

In an electrical system, the voltage at any point in the system can be thought of as analogous to the pressure in our heating network, and the current as analogous to the air flow. Just as the blower created air pressures above the normal atmospheric level, a battery or an active power supply is used to obtain voltage levels above some background reference point usually referred to as ground level or simply a ground. By allowing current to flow from the power supply to ground through appropriately chosen electrical resistors, we can obtain any desired voltage levels in this range to be used for whatever purposes we require.

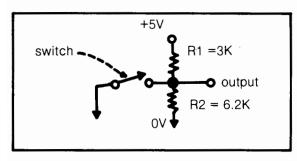

An example of this is shown in Figure I-10. At the top of the circuit we connect a 5 volt power supply, and the triangle at the bottom is a common symbol used to represent a ground point (i.e., a voltage level of zero).

Current flows through the two resistors (R1 and R2) establishing some intermediate voltage level at the output. the formula for calculating this output voltage is given by

$$V_{out} = V_{in} \cdot \left(\frac{R2}{R1 + R2}\right)$$

Using the values of  $V_{in} = 5$  volts, R1 = 3K (resistances are measured in units called ohms, and K is an abbreviation for kilo-ohms = 1000 ohms), and R2 =6.2K, we obtain a value for the output voltage of approximately 3.4 volts. If we now connect the output point to ground through a switch, by opening and closing this switch we can change the output voltage from 3.4V to 0V. That is, when the switch is closed, the resistance in this path is almost zero (only the small resistance of the wire itself) and practically no current flows through the R2 path. Thus the entire 5 volts is dropped by R1 leaving the voltage at the output point zero.

If we now run a wire from the output point to someone who has a voltage measuring device like a voltmeter, as we open and close the switch he will see his voltmeter register 3.4V and 0V alternately. And if we now agree on some meaning to be assigned to the high and low voltage levels, we can use this electrical circuit to transmit information.

For example, the flag line of the interface card uses the high voltage level to indicate busy, and the low level to indicate ready. And rather than the mechanical switch, the interfaces employ electronic devices called gates to switch between high and low levels at electronic speeds. These gates will be discussed later in this section.

The signaling scheme described would work just as well using other values for the power supply voltage, resistors, and output voltage. The example values given were chosen because they correspond to the socalled TTL (Transistor Transistor Logic) levels that are in common usage in computer hardware. Prepackaged integrated circuits are readily available which are used in generating and detecting high and low voltage levels, and in performing certain "logic" operations on these signals as will be discussed later. These chips or IC's as they are called, are made up of a large number of transistors and other electronic elements reduced to a very small size and sealed in convenient packages. It is the electrical properties of these transistors that dictate the high and low voltage levels that must be used. In general, it is very difficult and expensive to provide circuits that will provide and detect exact voltage levels. Therefore, TTL devices allow a range of voltages given by the table in Figure I-10a.

| = 3 volts | to 5 volts     |

|-----------|----------------|

| = 0.7 vo  | lts to 3 volts |

| = 0 volts | to 0.7 volts   |

|           | = 0.7 vo       |

| Figure I- | 1 | 0a |

|-----------|---|----|

|-----------|---|----|

The exact values of the crossover voltages vary with the type of IC used and with the manufacturer, but are typically within a few tenths of a volt of the levels given. Output voltages in the indeterminate range may result in the detecting IC sensing a high or a low, and should be avoided when designing TTL circuits.

Because the interface is implemented in terms of high and low voltage levels and the computer deals with bits (ones and zeros), there are two ways of assigning a correspondence between them. That is, we can assign either high=1 and low=0, or high=0 and low=1. Both methods are in common use, and the choice of one or the other is usually determined by other design considerations within the computer. Further confusion can arise since these two states are also refered to as true or false. This is why in the previous sections when concepts such as handshake were discussed, we simply referred to the states of the control and flag lines by their logical meanings of set or clear, and ready or busy, without worrying about whether these states were implemented as high or low voltage levels on the interface itself. Indeed, some interface cards allow the user to define whether the ready state of the flag line, for example, will correspond to a high or low level. This places fewer constraints on the design of the peripheral being interfaced and is discussed further in the section on jumpers.

Because these two conventions are in common use, they have been given the names positive-true logic and negative-true logic. The table in Figure I-11 shows the meanings of these conventions.

Positive-True Logic: High = True = 1 Low = False = 0 Negative-True Logic: High = False = 0 Low = True = 1

Thus if the computer placed a bit that was set to a one on a particular data line, this line would be set high in a positive-true system and low in a negative-true system. For example, an ASCII "E" character (binary value 01000101) placed on the data lines would appear as LHLLHLH if positive-true logic were being used, and as HLHHHLHL if negative-true logic were being used.

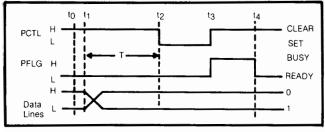

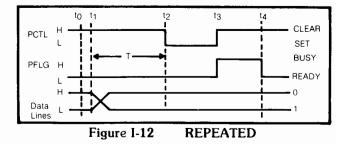

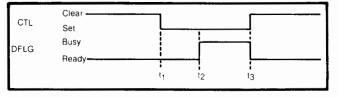

Certain interface processes such as the handshake discussed in the previous section involve several lines changing their states in a definite time sequence. The exact relationship of these lines during the sequence of events is often shown in a graphical representation called a timing diagram. An example of a timing diagram for some of the lines involved in the handshake process for the 98032A interface is shown in Figure I-12.

Figure I-12: An Example Timing Diagram

In this diagram, time proceeds along the horizontal axis from left to right, and the states (high/low) of the various lines of interest are shown one above the other. A vertical line drawn through the diagram represents the same instant in time for all of the lines. These time points may be indefinite such as to in the example which shows the state of the lines at some time before the handshake has begun; or they may be definite times such as t1 which shows the point at which the data on the lines begins to change. Sometimes, the interval between two time points (t1 and t2 in the example) is fixed by some requirement of the system, and given a name such as T. In other cases, such as the interval between t2 and t3, there is no restriction placed on the time that may elapse between these two events.

The state of the PCTL and PFLG lines in the example are definite (high or low) within each time interval. The handshake timing diagram cannot, however, show the data lines as being either high or low during a given interval, since the state of these lines depends on the data that is being exchanged. In this case, the two parallel (high and low) lines in the diagram simply represents a stable state on these lines that may be either high or low, while the crossover represents the time during which data on these lines is in a state of transition.

The example timing diagram for an output handshake process would be read as follows. At some time to before a data transfer has begun, the PCTL line is in its

normal clear state (high), the PFLG line is ready (low), and the data lines are stable, still containing the last character sent. At time t1 the interface places the new data on the lines. After allowing a time interval T for the data to become stable, the interface sets PCTL low at t2 to inform the peripheral that the data on the lines is valid. Longer cables require longer time periods, T, for the data lines to stabilize at their new levels. After an unrestricted time interval, the peripheral acknowledges that it has seen control go set by raising its PFLG line to the busy state at t3. Upon receiving this acknowledgment, the interface allows its PCTL line to return to the clear state. Finally, when the peripheral has completed processing the information on the data lines, it indicates this fact to the interface by returning its PFLG line to the ready state at t4. At this time, the PCTL and PFLG lines are back to the same state as they were at to and ready to repeat the entire handshake cycle for the next data transfer.

The complete handshake process also involves the FLG and I/O lines as discussed in the section on the 98032A interface. This simplified example is intended merely to present the essential features of timing diagram representations.

# 2. Gates, Latches, and Flip-Flops

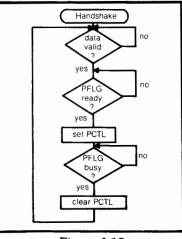

It would be extremely difficult if not impossible to write useful computer programs without the availability of conditionals such as the "if" statement which allow the program to test some condition and perform one action if the condition is true, and another action if it is false. The operations performed by an interface card also require the use of logic, or the ability to make decisions. The functions of the interface card could be fully described by a flowchart or a computer program. Indeed, if it were not for speed requirements, most of the functions of the interface card could actually be replaced by a computer program. For example, the handshake process described in the last section could be performed by a program which implemented the flowchart shown in Figure I-13.

Figure I-13

#### Gates

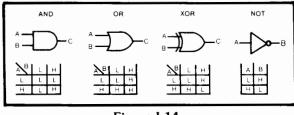

Since the interface cards are implemented through hardware (electronic circuits) rather than software (computer programs), logic elements called gates are used to perform the required decisions. In reality these gates are made up of very complex electronic networks composed mainly of resistors and transistors. Fortunately, it is not necessary to understand the detailed workings of these circuits in order to present the operational characteristics of these logic elements. Before looking at how these gates are used in the construction of an interface, we will first describe the various types of gates that are available. Figure I-14 shows four of the basic logic elements that are used as building blocks for constructing more complex logic elements and implementing conditional operations.

For the AND gate, A and B are the inputs and C is the output. It performs a logic AND function since C is high if and only if both A and B are high, otherwise, C is low. This information is presented below the symbol for the AND gate in a form called a truth table. It simply shows the state of the output line for any combination of states of the input lines. In the OR gate (sometimes called an inclusive OR gate), C is high if either A or B is high. In the exclusive-OR gate, C is high if either A or B is high, but not both. And finally the NOT gate, often called an inverter, outputs a high if the input is low, or a low if the input is high.

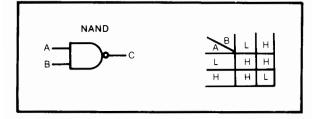

Several gates of the same type can be obtained in a single integrated circuit package which makes the construction of logic circuits such as an interface card more compact and less costly than if individual components were used. Also available are packages which combine AND, OR, and Xor gates with inverters on their input lines, their output line, or both leading to a wide variety of combinations. For example, AND gates with inverted outputs are available and are called NOT-AND or simply NAND gates. Figure I-15 shows the symbol and truth table for this type of gate.

Figure I-15

Notice that the truth table is the one that would be obtained by inverting the output of an AND gate. In general, the truth table for any logic element whose input or output lines have circles drawn on them can be obtained from the corresponding table for the element without the circles, and replacing the circles with inverters.

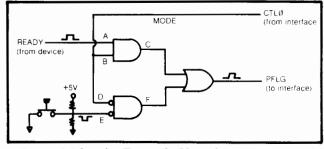

An example will serve to illustrate how these logic elements are used as building blocks in constructing circuits that are capable of making decisions. Let's assume that we have a peripheral that delivers data to the computer at some time after it sees the control line (PCTL) go set. Normally, this operation is automatic so that as soon as control is set, the device reponds by issuing a pulse (low to high and back to low transition) on a line from the peripheral called READY. This READY line would usually be connected directly to the PFLG line on the interface to complete the handshake. But we would like to have an alternate mode of operation. established by the computer program, that would allow an operator at the device to signal the ready response by pressing a button. The circuit shown in Figure I-16 could accomplish this task, making use of the logic elements that we have been discussing.

We first define a MODE line which determines the mode of operation: automatic when it is high, and operator-controlled when it is low. This line is connected to one of the general purpose control bits (CTLØ on the 98032A card) so that it may be set by the program to the desired mode of operation. When MODE is low, the input to the AND gate at pin B is low so that no matter whether A is high or low, the output at C is low. That is, when mode is low (operator control) the READY pulse is blocked by the AND gate and C remains low. When mode is high, C is high only when A is also high, so that the positive pulse is now passed by the AND gate and appears at the output C.

Figure I-16: An Example Use of Logic Elements

The second AND gate controls the signal from the operator's push button. When the switch is open, the pull-up resistors hold the input E high (see Figure I-10). Pressing the button grounds the input E and causes it to go low, returning again to high when the button is released. (In actual use, a debounced switch should be used to prevent multiple pulses.) Since the input E is

an inverted input, this switch presents a positive pulse to the AND gate when it is activated. Input D operates in the same way as input B did for the READY pulse, to either block or pass the signal from input E. But since it is an inverted input, it passes the signal when MODE is low and blocks it when MODE is high. Thus, either the READY pulse or the one provided by the push button will appear at C or F, while the other line remains low. If these two lines are connected to the PFLG line through an OR gate, one and only one of the pulses will drive PFLG, depending on the state of the MODE line.

Thus, this configuration of logic gates implements the function stated by: if mode is automatic, pass the READY pulse to the PFLG line and block the pulse generated by the operator; if mode is manual, pass the operator's pulse and block the READY signal. Again we see that gates are used to provide a hardware implementation of a function that could be expressed by a logical flow diagram.

#### Latches

If the data output lines from the computer were directly connected to the data input lines to the peripheral, then during the handshake process it would be the responsibility of the computer to maintain the data on the lines until the peripheral had acknowledged that the data had been accepted. Normally this would cause no problem since the computer is merely waiting anyway for that acknowledgment so that it can put the next data item on the lines. But if only one character is being sent, the computer could go on with the program if it did not have to stay in the output driver to hold the data on the lines. This becomes more important, even essential, to operating under interrupt. In the interrupt mode, the computer places the first character of the output message on the data lines, tells the interface to generate an interrupt when the peripheral has taken that character and the next one can be sent, and then goes on with program execution instead of waiting for the handshake process to complete. This would not be possible if the computer had to maintain the data on the lines.

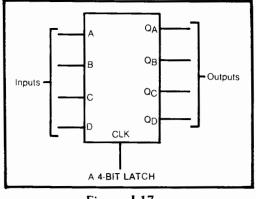

Therefore, one of the functions of the interface is to be able to hold or latch the information on the data lines until the peripheral has had a chance to take it, and thus relieve the computer of this responsibility. In the hardware of the interface, this is accomplished through an electronic device called a latch (Figure I-17). Typically a latch has a number of input lines and a corresponding number of output lines, plus an additional line usually called the clock line. When the clock line is activated, whatever data currently is being presented on the input lines is held by the latch and presented on the output lines. Then when the clock line is deactivated, this same data is maintained on the output lines. The way in which the clock line is activated (i.e., positive pulse, negative pulse, low to high transition, etc.) depends on the particular type of latch being used, and need not concern us here.

Chips are available which provide latching for four bits of data on a single integrated circuit package. Thus, to provide latching for the 16-bit output data bus, the 98032A interface uses four of these 4-bit latches. Four more are used for the 16 data input lines. These input latches, in a manner similar to the output operation, relieve the peripheral of the responsibility of maintaining the data on the interface input lines until the computer has had a chance to take it.

These latches are sometimes refered to as one-character buffers, and should not be confused with the buffers described in later sections dealing with the transfer of interrupt buffers. These latter buffers are multi-character holding locations that are located in the read/write memory of the computer itself.

#### Flip-flops

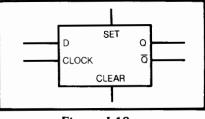

A flip-flop is a device that is similar to a one-bit latch, but with more extensive control properties. There are many different types of flip-flops each designed to satisfy a different set of requirements. Figure I-18 shows a schematic representation for one common type called a D-type flip-flop.

Figure I-18

When the clock line is activated, the current state of the D input is latched and presented at the Q output line. On deactivating the clock signal, Q will hold its state independently of what happens on the D input. For convenience in designing logic networks using these flip-flops, an inverted output,  $\overline{Q}$ , is also provided. that is,  $\overline{Q}$  is always in the opposite state from that of Q. Two additional lines are provided to set Q to the high state or to clear Q to the low state, independently from the clock and D lines. These set and clear lines are often used to initialize the flip-flop to the desired "wake up" state.

Just as the latches were used to maintain information on the data lines, flip-flops are used to allow the interface to "remember" information about what state it is currently operating in. For example, we will see later that the computer will send a particular message to the interface card to tell it that it is enabled to operate in the interrupt mode. The card remains in this mode until it is disabled by another message from the computer. In the meantime, it remembers which mode it is in (enabled or disabled) by storing that information in one of these flip-flops.

## 3. The Use of Jumpers

In the last section we saw that flip-flops could be used to change various modes of operation on the interface by programmable signals from the computer. For example, the interrupt-enable flip-flop could be turned on and off by the computer at will. Other modes of operation are a property of the system itself and do not change during the running of a program. It would be more convenient if these modes could be set one time on the card itself, and then the program would not have to be concerned with them.

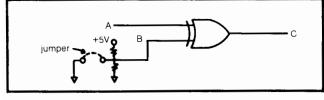

As an example of this, consider the handshake diagram from Section IC1. The meaning assigned to the PFLG line from the peripheral is high = busy and low = ready. We might want to interface a device, however, whose handshake line used the opposite sense; that is, high = ready and low = busy. The 98032A card provides for such an inverted sense by installing a jumper (i.e., a wire connecting two terminal points in the circuit) on the interface itself. Figure I-19 shows how the use of this jumper accomplishes the desired inversion of the PFLG signal.

Figure I-19

The properties of the exclusive-OR gate used were given in Section IC2. Its output, C, is high if either A or B is high but not both. If the jumper is not installed, the resistive divider holds the B input high. Looking at the truth table for an exclusive-OR gate, we see that in this case if A is high, C is low; and if A is low, C is high. Thus, the signal presented at the A input appears inverted at the C output. If we now put in the jumper, the B input is connected to ground (low) and the state of C is always the same as the state of A. As a result, the signal seen at C is either the same as A or the complement of A depending on whether the jumper is in or out.

It should be noted that in the particular example used, (i.e., the PFLG line on the 98032A card), this line has already gone through a separate inverter gate before arriving at the A input line in our diagram. As a result, the PFLG line itself is inverted when the jumper is installed, and not inverted when the jumper is out.

Other jumpers may be used in an entirely different way from the example just given. For instance, we will see later that the data latches on the 98032A interface are divided into two groups of eight. In the so-called bytes mode, these two groups of latches can be clocked separately, while in the words (16-bit) mode, they are clocked together at one time. The jumper which selects the word mode simply connects the two clock signals for these latches together.

Finally, we should mention that the use of jumpers provides a means of making these connections in a manner that is most economical of space on the interface card. On other cards where room is available, miniature slide switches may be used to achieve the same result. Also, switches are used instead of jumpers where the user might want to change the mode of operation based on the particular application. In any case, these switches and jumpers are used to select modes that will not be required to change during the running of a particular program.

The installation and service manuals for each interface card go into more detail on the switches and jumpers provided by each card, and their intended uses. The purpose of this section is merely to give the reader some idea of how a jumper or switch can be used to perform the functions described in those manuals.

# Section II Programming for Interface Operations

# A. Standard I/O Programming

# 1. A Register Operational Model of an Interface

An interface is a complex electronic circuit that provides mechanical, electrical, data format, and timing compatability between a computer and the peripheral device to which it is connected. From a programmer's point of view, however, the primary task of interfacing is to provide a means of exchanging data between the computer and the peripheral. Thus, a well-designed interface should isolate the programmer from the details of the electronics and timing, and appear as a simple "black box" whose I/O characteristics can be presented in a simple model and described by a set of operational rules.

In Section III, we will look at the various interfaces provided for HP desktop computers from a hardware point of view and cover some of the special characteristics of each of them. In this section, it will be sufficient to model the interface as a set of four registers through which all the capabilities of the card can be accessed. These four registers are given in Figure II-1.

| Register | Input             | Output             |

|----------|-------------------|--------------------|

| R4       | Primary Data In   | Primary Data Out   |

| R5       | Status In         | Control Out        |

| R6       | Secondary Data In | Secondary Data Out |

| R7       | Secondary Status  | Secondary Control  |

|          |                   |                    |

Figure II-1

The names of the four registers (R4,R5,R6, and R7) are simply names given to four address locations in the computer memory map, and should not be confused with the r-registers which are program variables provided by the high-level HPL language. These registers

should be thought of as residing on the interface card itself.

The computer sees these interface registers as 16-bit, binary registers, and always sends and receives 16-bit binary words when addressing them. If a particular interface utilizes less than the full 16-bits (for example, when exchanging 8-bit ASCII data bytes) the upper (more significant) bits are received as zeros. On output to these registers, if fewer than 16 bits are utilized by the interface, it ignores the upper bits. Thus, these bits may be ones or zeros and are sometimes called "don't care" bits.

All of the interface cards use the R4 register for data I/O operations, and the R5 register for status and control information. The names given in the table above for the R6 and R7 registers are only general indicators of the functions of these registers. Their exact interpretation varies with each card and is described in more detail in the sections on the individual interfaces.

In order to give specific examples of the use of these I/O registers, we will use the meanings given to them by the 98032A Bit Parallel Interface, sometimes called the GPIO (General Purpose Input Output) Interface. It defines these registers as follows.

| Register   | Input      | Output      |

|------------|------------|-------------|

| R4         | Data In    | Data Out    |

| R5         | Status In  | Control Out |

| <b>R</b> 6 | (see text) | (see text)  |

| R7         | Not Used   | Trigger     |

#### Figure II-2

The GPIO uses the R6 register in a special way when operating in the optional "byte mode" as described in the section on that card. For our purposes here, the R4 register is the one through which all data is transmitted and received. We will give examples below of how these registers are used to do simple input/output operations.

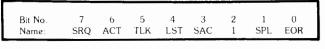

### 2. Select Codes

As mentioned earlier, a set of I/O registers R4-R7 exist on each interface card. When more than one card is connected to the computer and, for example, an R4-in operation is performed, we need a mechanism for determining which interface should respond. This is accomplished by means of a 4-bit register in the computer called the Peripheral Address (or simply PA) register. This PA register holds a binary number in the range of 0 to 15, thus allowing for up to 16 interfaces to be addressed. Each interface has an externallysettable select code switch which can also be set to any value between zero and 15. (Select codes 0 and 1, however, are for internal interfaces and should not be set as a select code for an interface card.) Whenever an operation to one of the interface registers is performed, the computer presents the current contents of the PA register to all of the interface cards simultaneously. Only that card whose select code matches the PA register will respond to the operation.

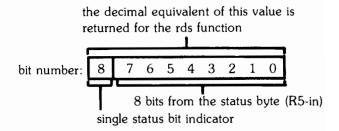

When an HPL I/O statement such as "wrt 6, A, B, C" or "rds(6)  $\rightarrow$  A" is executed, the I/O ROM automatically puts the binary value of the select code parameter (in this case, 0110 = 6) in the PA register before addressing the required interface registers.

## 3. Direct Register Access

All interface card operations are carried out by sequences of operations to and from the interface registers. The more common tasks (reading and writing data, checking status and setting control bits, etc.) have been provided at the HPL programming level by simple statements and functions such as wrt, red, rds, wtc, etc. These high-level mnemonics isolate the programmer from the details of the register sequences required to perform each task.

In the event that the programmer should wish to perform some sequence of operations other than those provided by the HPL language, additional mnemonics have been provided that give the HPL program direct access to the interface registers.

These are the write-interface-register and the readinterface-register mnemonics, whose syntax is given below.

> wti <register number>, <output> rdi (<register number>)

The write-interface statement outputs a 16-bit, 2's-complement representation of the value specified by the <output> parameter to the register specified. The read-interface function inputs a 16-bit 2's-complement binary value from the specified register and returns its decimal equivalent for the value of the function. The register number given should be in the range of 4 to 7. If not, the value given is mapped into that range. Thus, rdi(8) would read the R4 register, rdi(9) the R5 register, and so on. Since the program needs some way of specifying which interface (select code) should respond to wti and rdi, register number zero is treated specially and addresses the PA register. For example, executing a "wti 0,6" statement would place a 6 in the PA register. This setting of the PA register will remain active for all future wti and rdi operations until RESET is pressed or a new PA is set up using another wti statement to register zero.

In the following section, we will see how this direct register addressing works by reducing familiar operations such as writing data and reading status to their equivalent register sequences.

Before doing this, there are two additional lines to the interface required to complete the functional description of the card. These may be considered as 1-bit, read-only registers called status (STS) and flag (FLG).

The status bit (not to be confused with the status register, R5 to be discussed later) is a single bit indicator that the interface and the peripheral connected to it is operational. For example, if a peripheral device has a line coming from it that indicates power on, it could be connected to the STS line. Then the program could quickly determine whether the device is turned on or off. Or as another example, a printer might have the STS line connected to its out-of-paper indicator (if it has one) to indicate to the program that it is no longer operational when the paper runs out.

The flag line is a momentary ready/busy indicator used to keep the computer from getting ahead of the peripheral. The use of this line is covered in more detail in Section IIIB2 on "handshake". For our purposes here, it is sufficient to know that on the flag line, a one indicates ready and a zero indicates busy. For example, if the computer had a sequence of ASCII characters to send to a slow printer, it would send one character (which makes the flag line go busy) and then wait for the flag line to go ready again before sending the next character. (This interface flag indicator should not be confused with the programming flags used in writing HPL programs.)

These FLG and STS lines may be tested from the HPL program by using the following functions.

iof <select code> ios <select code>

These functions return a one or a zero indicating the current state of the FLG or the STS line. Notice that unlike wti and rdi, the select code is given as a parameter in the iof and ios functions.

## 4. Binary I/O Operations

We are now in a position to look at the sequence of events that takes place between the computer and the interface card when simple I/O operations are carried out. In particular, we will simulate the actions of the "wtb" and the "rdb" statements through the use of the direct interface access mnemonics explained in the last section.

When the I/O ROMs perform these operations, there is a considerable amount of checking and internal "bookkeeping" that goes on to insure that systems conflicts are avoided. Here we will only be concerned with the basic communication between the computer and the interface. We will also look at this communication from the point of view of the register operational model of the interface as described earlier. In the sections on the interface cards themselves we will look at more detail about what actually takes place on the card.

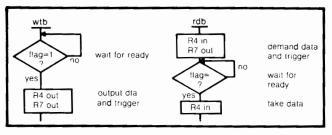

The following HPL program simulates the actions that take place when the statement "wtb 6, 27" is executed to send the binary value 27 to a device on select code 6.

wti 0,6

if ios(6)=0; gto "card down"

if iof(6)=0; jmp Ø

wti 4,27

wti 7,0

In the first line, the select code of the device (i.e., 6) is placed in the PA register for the subsequent wti statements. Next, the status bit is tested to make sure that the device is operational. If it is not, we branch to the "card down" routine, which in the I/O ROM would issue an error G8. If the device is operational, we then loop until the flag line indicates ready. The data to be sent is then placed in the R4 output register. This merely places the data in the output latches on the interface but no output operation to the device has taken place yet. In the last line, the output to the R7 register actually triggers the data transfer to the device. (Note that the actual data to the R7 register, a zero in this example, does not matter. Only the R7 out operation itself is sensed by the interface as the trigger command.) If more data were to be sent to the same device, we would repeat lines 2, 3, 4 and 5 for each data item. It is important that each time through this loop we wait for the flag to indicate ready. If the flag is indicating busy, the last data item is still in the output latches and has not yet been taken by the device. If we were to execute line 4 in this state, the new data would overwrite the old data in the latches and the old data item would be lost.

We can also use the direct register operations to simulate the input process. The following HPL program

performs the same operations as when the function "rdb(6) $\rightarrow$ A" is executed to read a binary value from the device on select code 6 and assign it to the variable A.

wti 0,6

if ios(6)=0; gto "card down"

if iof(6)=0; jmp 0

rdi(4) → A

wti 7,0

if iof(6)=0; jmp 0

rdi(4) → A